Solid State Circuits Society

IEEE Santa Clara Valley Chapter

March 15, 2018 by Prof. David Patterson, Google, Mountain View

Thursday March 15, 2018, 6:00-8:00PM

Title: “50 Years of Computer Architecture: From Mainframe CPUs to DNN TPUs and Open RISC-V” by Prof. David Patterson, Google, Mountain View, CA, University of California, Berkeley, CA

Location: Texas Instruments Silicon Valley Auditorium

2900 Semiconductor Dr., Building E, Santa Clara, CA (Register here)

Date & Time: Thursday, March 15, 2018, 6:00 PM – 8:00 PM PDT

Location: Texas Instruments Building E Conference Center, 2900 Semiconductor Drive, Santa Clara, CA 95051

Directions: TI-BldgE-Auditorium.pdf

Registration Link: (Mandatory) : https://www.eventbrite.com/e/50-years-of-computer-architecture-from-mainframe-cpus-to-dnn-tpus-and-open-risc-v-prof-david-tickets-43815631734

Registration Fee: IEEE SSCS/CS/SPS/CIS members: free

Students – $3 (Register at Door $3)

IEEE (non-Society) members – $7 donation (Register at Door $10)

Non-members – $10 (Register at Door $15)

Abstract:

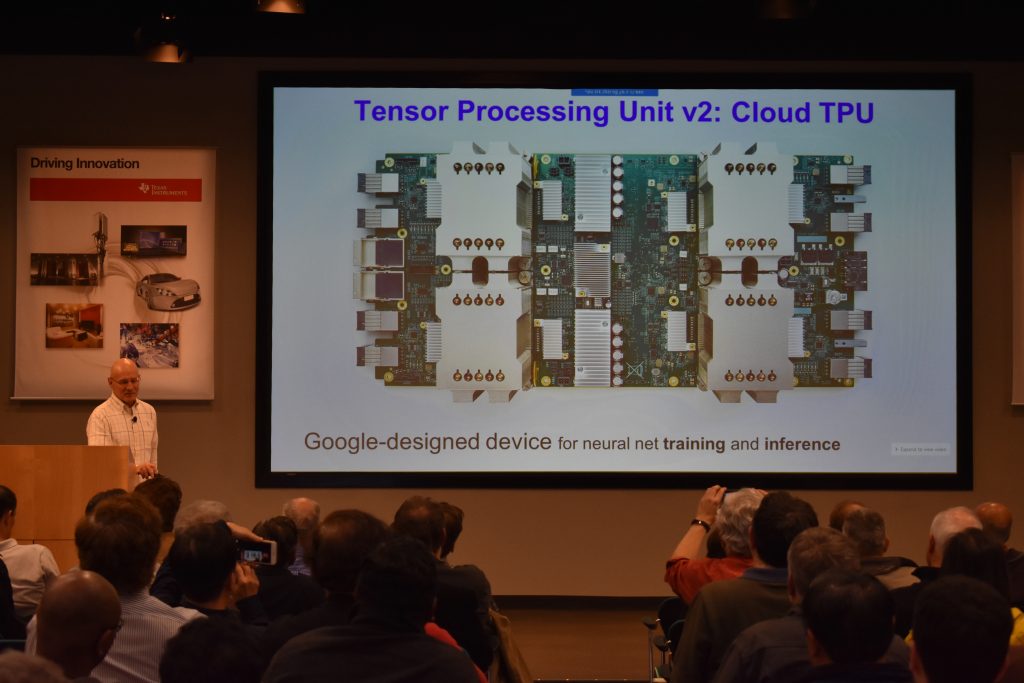

This talk reviews a half-century of computer architecture: We start with the IBM System 360, which in 1964 introduced the concept of “binary compatibility”. Next, came the idea of the “dominant microprocessor architecture”, for which the early candidate was the Intel 432 which was shortly replaced by the emergency introduction of the Intel 80×86 in 1978. However, for the next 20 years, the Reduced Instruction Set Computers (RISC) became dominant. Then, the Very-Long-Instruction-Word (VLIW) HP/Intel Itanium architecture was heralded as their replacement in 2001, but instead the role was usurped by AMD’s introduction of the 64-bit 80×86. Thus, while the 80×86 dominated the PC-Era, RISCs have led thereafter, currently with 20B shipped annually (versus 0.4B 80x86s). Since the ending of Moore’s Law and Dennard scaling has stalled performance of general-purpose microprocessors, domain-specific computer architectures are the only option left. An early example of this trend introduced by Google in 2015 is the Tensor Processing Unit (TPU) for cloud-based deep neural networking. The widespread agreement about instruction sets has led to the open architecture RISC-V (“RISC Five”), which has been embraced by more than 100 members of the RISC-V Foundation. RISC-V and accelerators like the TPU demark a new renaissance for computer architecture.

David Patterson is the Pardee Professor of Computer Science, Emeritus at the University of California at Berkeley, which he joined after graduating from UCLA in 1976. He is also a Distinguished Engineer at Google, where he helps with accelerators for machine learning.

Dave’s research style is to identify critical questions for the IT industry and gather inter-disciplinary groups of faculty and graduate students to answer them. The answer is typically embodied in demonstration systems, and these demonstration systems are later mirrored in commercial products. In addition to research impact, these projects train leaders of our field. The best-known projects were Reduced Instruction Set Computers (RISC), Redundant Array of Inexpensive Disks (RAID), and Networks of Workstations (NOW), each of which helped lead to billion dollar industries.

A measure of the success of projects is the list of awards won by Patterson and as his teammates: the C & C Prize, the IEEE von Neumann Medal, the IEEE Johnson Storage Award, the SIGMOD Test of Time award, the ACM-IEEE Eckert-Mauchly Award, and the Katayanagi Prize. He was also elected to both AAAS societies, the National Academy of Engineering, the National Academy of Sciences, the Silicon Valley Engineering Hall of Fame, and to be a Fellow of the Computer History Museum. The full list includes about 35 awards for research, teaching, and service.

In his spare time, he coauthored seven books, including two architecture texts with John Hennessy, who is past President of Stanford University. Patterson also served as Chair of the Computer Science Division at UC Berkeley, Chair of the Computing Research Association, and President of ACM.

Slides

Video

Photos

Welcome

Calendar

| M | T | W | T | F | S | S |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 | 31 | |