# Photonic Wire Bond Packaging for Silicon Photonics, Optical Fibers and Laser Integration

Lukas Chrostowski – Professor, Electrical and Computer Engineering, University of British Columbia – Co-founder, Dream Photonics Inc. October 19, 2023 IEEE EPS Bay Area Chapter

# Land Acknowledgement

3

#### Abstract

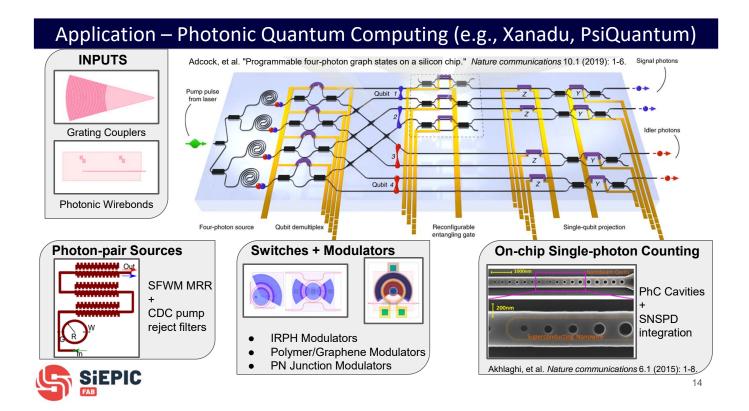

Photonic integrated circuit technology (silicon photonics) is used for many applications including optical data communications, optical and quantum computing, and sensing including LiDAR, biomedical and environmental. A major packaging challenge facing the industry is optical coupling between multiple integrated photonic components together with low insertion loss, in a cost effective manner, into a package suitable for commercialization. A promising approach is to create "photonic wire bonds" (PWBs), namely optical waveguides that look similar to conventional electrical wire bonds. PWBs are a high-yield, low-insertion-loss, and high-throughput versatile method of packaging photonic components such as chip-to-fiber, laser-to-chip interconnects. Utilizing two-photon polymerization to fabricate freeform 3D polymer structures, PWBs can connect components with arbitrarily disparate mode field shapes and sizes. Capabilities and advantages of the PWB technique include: gain chip integration with existing 'known good die', dense optical I/O connections to the chip, scalability from prototyping to high-volume, and interconnects that are not possible with other standard photonic packaging techniques.

# Outline

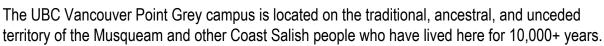

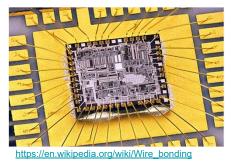

- Electrical wire bonding

- Challenges in packaging for photonics

- Silicon photonics introduction

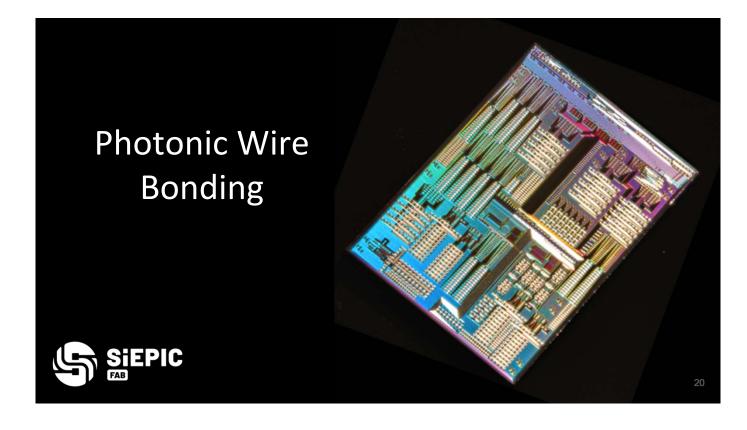

- Photonic wire bonding

- Commercial availability

#### Electrical Wire Bonding – impact on CMOS industry

- Invented in 1957 at Bell Labs

- Kulicke & Soffa (K&S) in 1959 developed the first commercial wire bonder 0

- Wire bonding fuelled the microelectronics revolution

- Whatever was not available on a CMOS chip, one can hybrid integrate on 0 a PCB

- Flexible

- Type: Ball, wedge

- Material: Copper, gold or silver

Bond pad pitch: from 30 to 100s µm

Number of bonds: e.g., 2, 50, 2000

- From Prototyping to Production

- Manual R&D tools 0

- High volume production lines with many wire bonders and robots, used for 0 smartphones, etc.

- Advanced packaging was forecast to replace wire bonding

- Flip-chip, TSV, Interposer, etc. 0

- Yet, wire bonding continues to be a workhorse 0

- And keeps improving: stacked die, multi-row connections

# Challenges in Packaging for Optics and Photonics

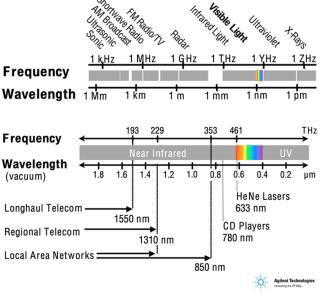

# What is a Photon?

- Electrons vs Photons

- Electricity "flows" anywhere there is a metallic contact

- A photon is a "wave"

- Electromagnetic

- Properties

0

0

- Wavelength

- (or Frequency or Energy)

- Waves are complex

- Amplitude

- Phase

- Spatial distribution

- "Mode" in a waveguide

- Temporal distribution

www.ieee.org/scveps

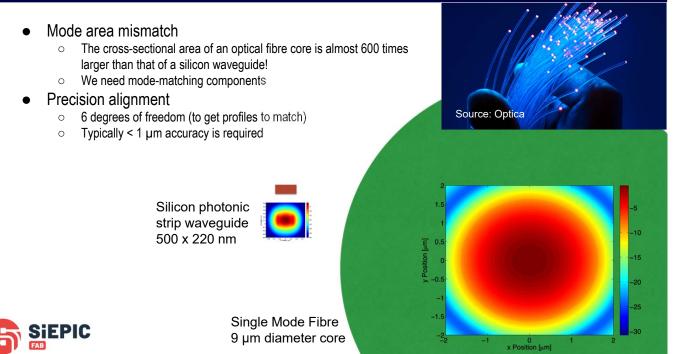

# Packaging challenges in Optics & Photonics

11

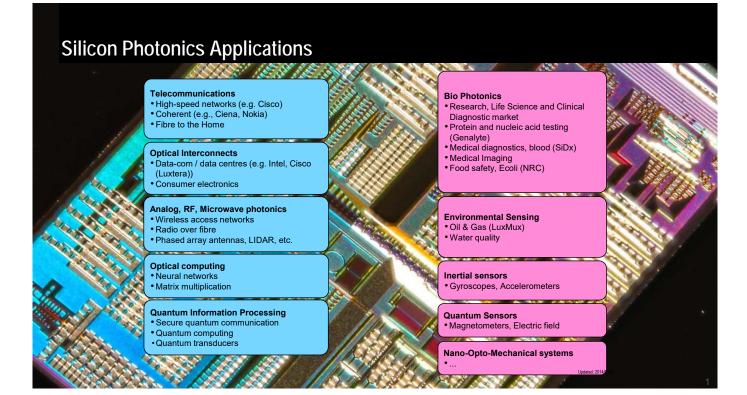

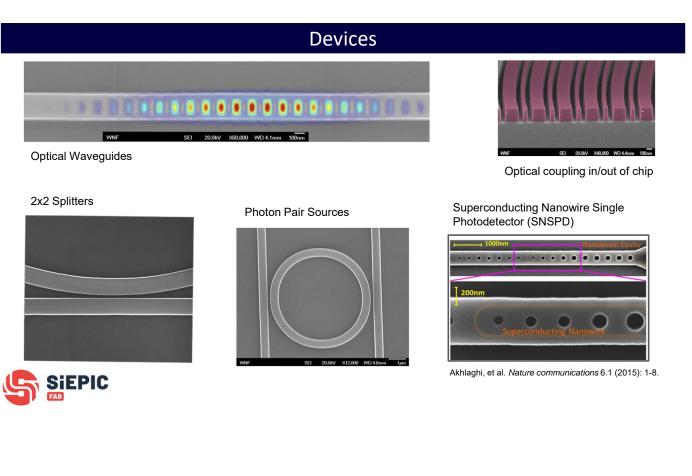

#### Silicon Photonics – Motivation

- Silicon electronics industry

- \$40+ Billion annual R&D investment\*

- Mature materials, processing, design technologies

- Possibility of leveraging this technology for optics/photonics

- Silicon photonics

- "integrated optics" and "photonic integrated circuits (PICs)" on silicon

- use silicon for optical waveguides and for optical processing/switching

- Small size, CMOS compatible

- Both electronics & photonics:

- electronic and photonic integrated circuits (EPIC) in silicon

- Also need rapid prototyping

\* \$53B in 2012. Source: IC Insight, and http://www.electroig.com/articles/sst/203/02/semiconductor-ra

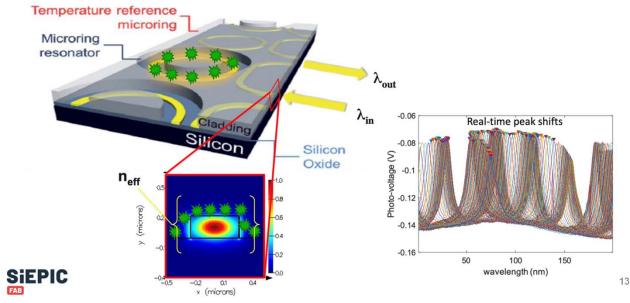

# Application – Silicon photonic evanescent-field ring (bio) sensors

- Refractive index sensing using resonators

- track resonance frequency changes

Challenges in Packaging for Optics and Photonics

# Packaging challenges in Optics & Photonics

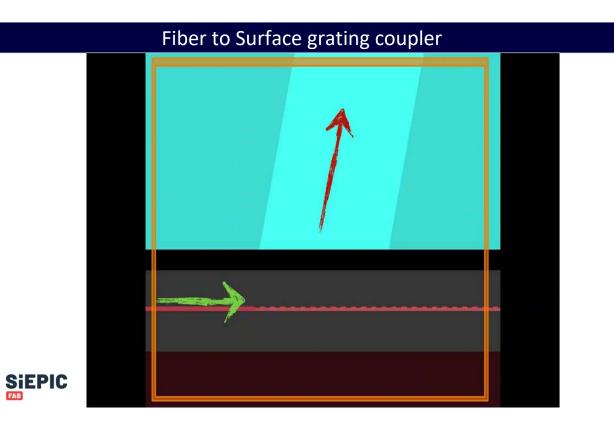

|      | Edge Coupling                                                 | Surface Grating Coupling                                         |

|------|---------------------------------------------------------------|------------------------------------------------------------------|

| Pros | Wide optical bandwidth                                        | Easy alignment                                                   |

| 1100 | <ul> <li>Support for both TE/TM polarization</li> </ul>       | Cost-effective – no post process                                 |

|      | Similar to existing laser & modulator edge                    | <ul> <li>Location flexibility in the designs; compact</li> </ul> |

|      | packaging techniques                                          | Chip/wafer scale automated measurement                           |

|      | High-efficiency                                               | High-efficiency                                                  |

| Cons | <ul> <li>Challenging alignment (smaller mode size)</li> </ul> | Limited optical bandwidth                                        |

|      | More complicated fabrication (e.g., edge facet                | Challenge in obtaining good coupling efficiency (typically       |

|      | polishing, tapers for mode expansion, access to               | 3 dB or more)                                                    |

|      | edge of chip)                                                 | Normal-incidence challenging for packaging                       |

17

# Packaging challenges in Optics & Photonics

- Desirable attributes for a photonic packaging solution:

- Whatever is not available on a silicon photonics chip, one can hybrid integrate

- Flexible

- Type: single mode, multi mode

- Pitch: from 30 to 100s µm

- Number of connections: e.g., 2, 50, 2000

- Works for a broad range of wavelengths

- Works for different types of chips (e.g., lasers)

- Temperature, Humidity, Shock, Reliability...

- Known-good die compatibility

- From Prototyping to Production

- Manual R&D tools

- High volume production lines with many wire bonders and robots, etc.

- Solution Photonic Wire Bonding

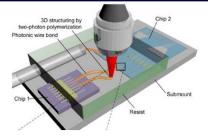

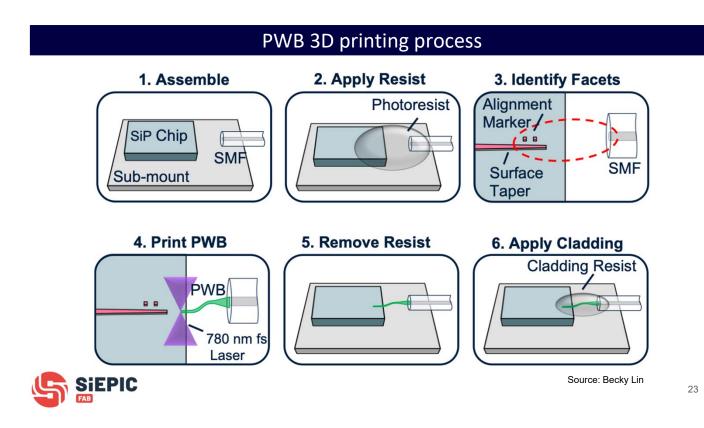

# Photonic Wire Bonding (PWB)

#### Packaging solution:

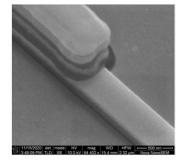

- Fast 3D fabrication of optical connection (30 to 120 seconds per bond) •

- Low optical insertion loss (< 3 dB per bond)

- High placement and optical misalignment tolerance (30 µm)

- Compact and mechanically stable (demonstrated down to 4 K)

- Flexible can accommodate components with disparate mode field size/shape .

- Low-volume prototyping, and potential for up to million units production

#### Vanguard Automation GmbH tool

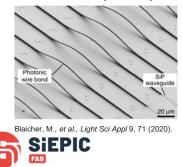

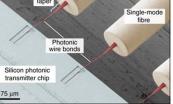

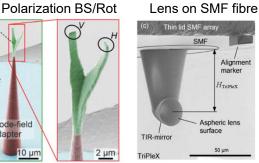

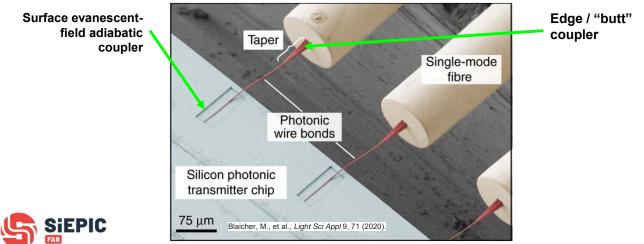

# Menagerie of photonic wire bond connections

DFB to SiP

Blaicher, M., et al., Light Sci Appl 9, 71 (2020).

PBS.

SMF

Mode field

adapt

10 µm

A. Nesic et al., arXiv 2107.12282 (2021)

SiP to SiP (reliable)

Tape

SiP to SMF fibre

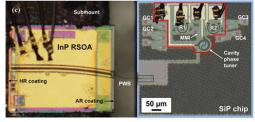

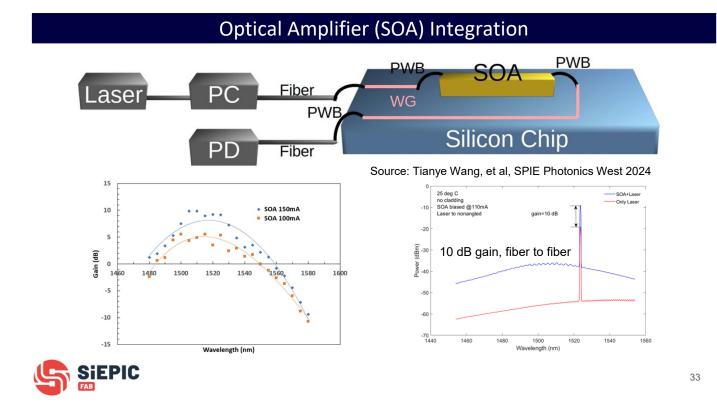

#### SOA to SiP - External Cavity Laser

Xu, Y., et al., Scientific Reports 11, 1 (2021).

#### Lens on SNSPD

M.Trappen, et al., *Opt. Express* 28, 37996-38007 (2020)

Y. Xu, et al., Opt. Express 29, 27708-27731 (2021)

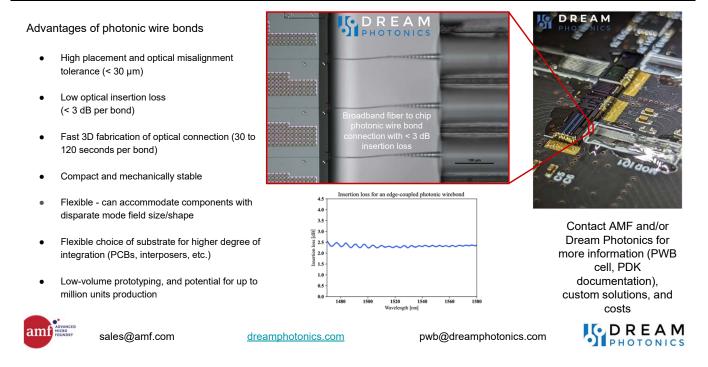

#### Fiber-to-chip packaging of AMF chips with photonic wire bonds (PWB)

DREAM PHOTONICS 4.0 3.5 Advantages of photonic wire bonds SED 3.0 uog 2.0 Fast 3D fabrication of optical connection (30 to 120 seconds per bond) 1520 1540 Low optical insertion loss • D R E A Μ (< 3 dB per bond) PHOTONICS High placement and optical misalignment tolerance (< 30 µm) Compact and mechanically stable Flexible - can accommodate components with Contact AMF and/or disparate mode field size/shape Dream Photonics for more information (PWB Low-volume prototyping, and potential for up to cell, PDK million units production documentation), custom solutions, and costs

sales@amf.com

dreamphotonics.com

pwb@dreamphotonics.com

PHOTONICS

#### Fiber-to-chip packaging of AMF chips with photonic wire bonds (PWB)

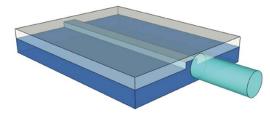

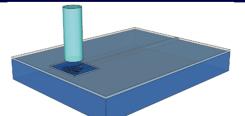

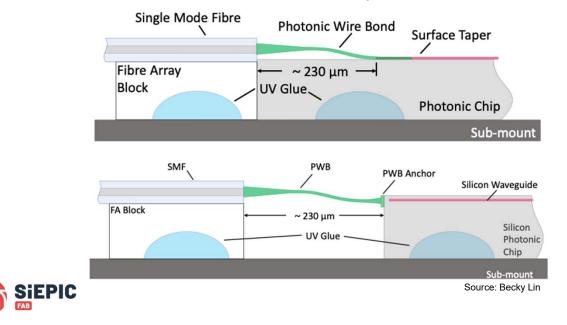

# Surface or Edge PWBs

PWBs can be attached to either the surface or the edge of a chip

# Surface or Edge PWBs

- Surface couplers require access to the optical waveguide

- Achieved using an oxide open process step

- Edge coupling requires a clean facet (etched or polished)

- Both interfaces have been shown for Si, SiN, and other materials

27

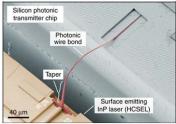

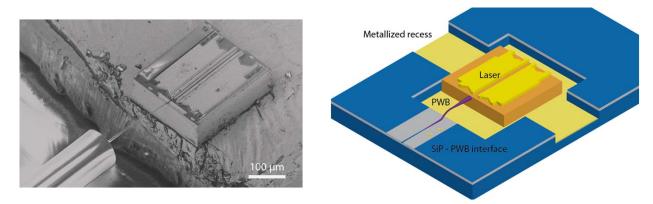

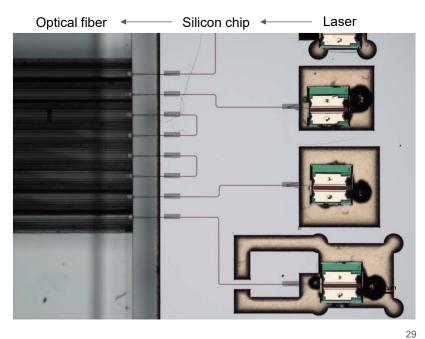

#### PWB interfaces - DFB laser to chip/fiber

Distributed feedback (DFB) laser placed in recess on the SiP chip, integrated via a PWB

Ref: "SiEPICfab: the Canadian silicon photonics rapid-prototyping foundry for integrated optics and quantum computing" SPIE 2021 https://www.dropbox.com/s/jutwul04a0zfl24/2021 SPIE PW SiEPICfab.pdf?dl=1 https://www.dropbox.com/s/2xvgjixu0ccghfs/SPIE PW 2021 SiEPICfab v2.mp4?dl=0

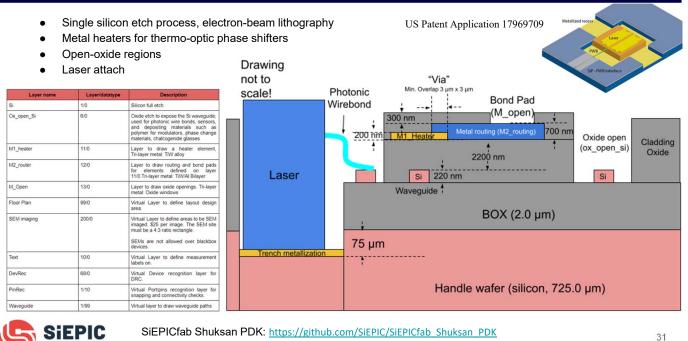

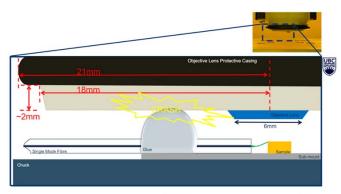

# Integrating a Laser on a Silicon Photonics Chip

In-house chip fabrication

- EBL + ICP-RIE for photonic layer

- Maskless lithography + DRIE for laser recess

- Ti/Au metallization of deep trench for probing/electrical wire bonding

Laser attach

Reflow soldering, laser placement with flip chip die bonder tool (~5 µm placement accuracy)

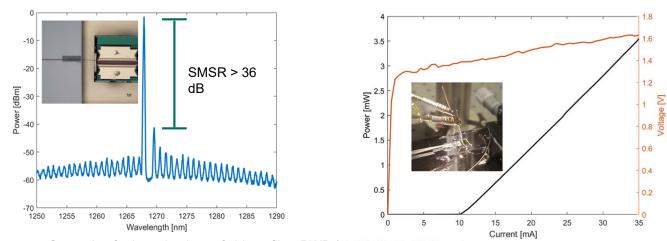

Integrating a Laser on a Silicon Photonics Chip

- Correcting for insertion loss of chip to fiber PWB (-2.25 dB @ 1270 nm):

Power coupled to the chip = 5.8 mW @ 35 mA, 59% ± 5% coupling efficiency laser to chip

- Good side-mode suppression ratio

- Excellent heat sinking to silicon substrate: current tuning coefficient 10 pm/mA

- Risk: No isolator optical feedback may degrade (or improve!) laser performance (linewidth, RIN)

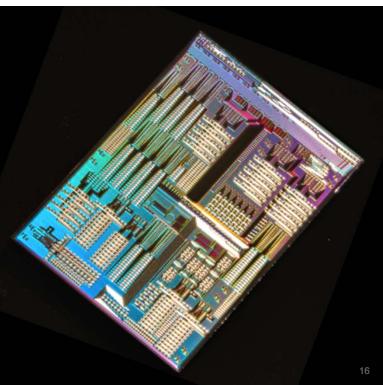

#### SiEPICfab Shuksan – Process Development Kit Overview: Layer Stack

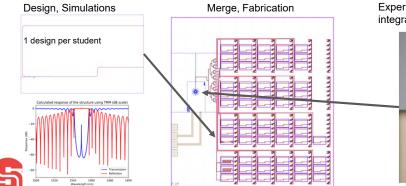

## Training on laser integration

- Offered the world's first undergraduate course (UBC ELEC 413) that featured a design-fabricate-test cycle with laser integration to silicon photonics.

- Less than 6 weeks! Student design submission Feb 18, 2023. Fabrication in Feb-March. Testing March 31, 2023.

- Goal: Design, simulate and layout a photonic integrated circuit containing a 1310 nm DFB laser attached to your own circuit, such as a resonator. Use the laser to characterize the circuit.

- Planning for a new online course "AIM Photonics-SiEPICfab: Semiconductor Laser Integration with Silicon Photonic Integrated Circuits". Target launch January 2025.

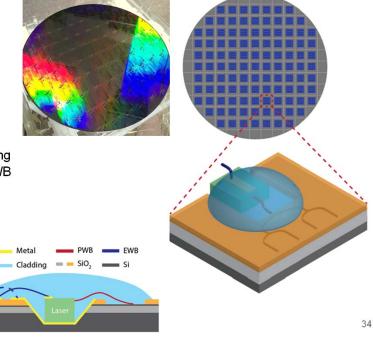

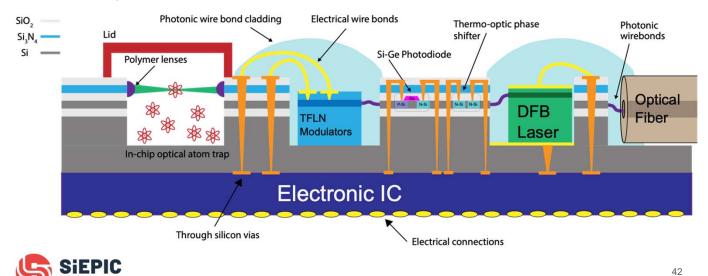

# Towards wafer-scale laser integration with foundries

#### Anticipated process steps

- 1. SiP wafer with metalized deep trenches

- 2. Pick and place lasers into trenches

- 3. EWB laser die to chip bond pads

- 4. PWB laser to PIC

- 5. Clad PWB and EWB

- 6. Dice

- Follow with remaining required packaging steps (Fiber array to chip assembly, EWB to PCB, etc.)

#### Writing speed

- 30 seconds per laser to chip bond

- 1000 lasers in ~8 hours

35

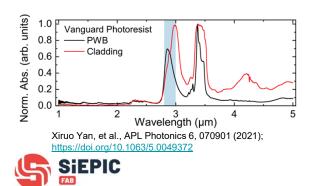

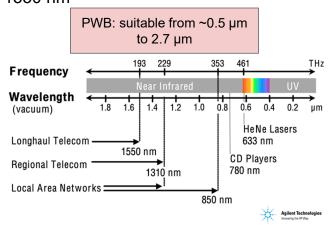

#### Wavelength

- PWB polymer material is transparent for green, red, infrared

Limit for visible applications: polymer starts absorbing ~ 450 nm

- VCSELs: 850 nm, 980, 1310, 1550 nm, etc

- DFBs for datacom/telecom: 1310, 1550 nm

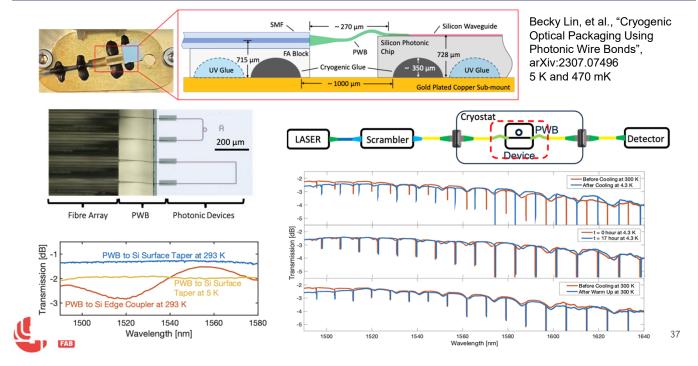

#### Cryo testing – using automated fibre array or photonic wire bonds

For Quantum applications

# Cryo testing – using automated fibre array or photonic wire bonds

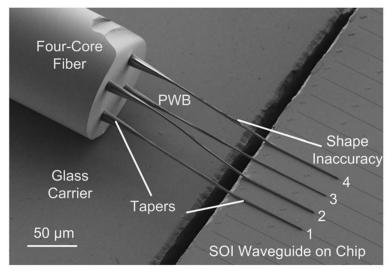

#### **Multi-core Fibers**

- Multi-core fibers are being considered for future high-density datacomm

- Demonstrated 1.7 dB coupling efficiency

Ref: N. Lindenmann, "Connecting Silicon Photonic Circuits to Multicore Fibers by Photonic Wire Bonding" IEEE JLT, 2015

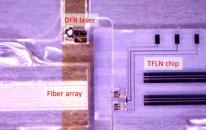

# Integration of multiple chips

- No single material platform offers all functionality. Can integrate:

- III-V lasers, SiP, thin-film Lithium Niobate, detectors, optical fibres...

- Example optical computing system, TFLN (Thin-Film Lithium Niobate) tested up to 65 GSa/s, with laser and detectors

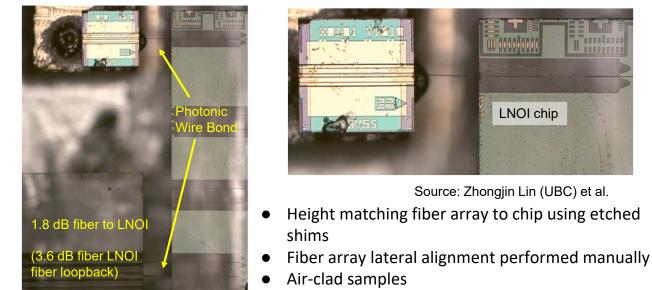

Source: Zhongjin Lin (UBC) et al.

Integrating a Laser with a LNOI chip (preliminary results)

• 1.8 dB coupling efficiency from fiber to TFLN

40

| EWB vs PWB            |                                                   |                                                                       |  |  |

|-----------------------|---------------------------------------------------|-----------------------------------------------------------------------|--|--|

|                       | Electrical Wire Bond                              | Photonic Wire Bond                                                    |  |  |

| Data signal bandwidth | Limited, typically tens GHz                       | Potentially very large with multiplexing (WDM), N x tens of GHz       |  |  |

| Flexibility           | Pad pitch, >30 μm                                 | Coupler pitch, >30 µm                                                 |  |  |

| Pad design            | Different sizes, different metals, ESD protection | Optimal surface or edge coupler cells                                 |  |  |

| Number of bonds       | 1 to thousands                                    | 1 to tens to hundreds (largest fiber<br>array is 256 on 127 μm pitch) |  |  |

| Speed                 | ~1 s per bond                                     | 30 s to 90 s (anticipate it will go down in next generation of tool)  |  |  |

| Volume                | Prototype to High Volume                          | Prototype to High Volume (not yet demonstrated)                       |  |  |

41

# Hybrid Integrated Photonics

Long term vision: photonics integration platform for various applications, mixing different types of materials

## Conclusions

- Photonic Wire Bonds have similar strengths as Electrical Wire Bonds

- First commercial PWB tool delivered in 2020 and most activities are in prototyping. Customers are interested in getting to high volume.

- PWB as a solution for optical fiber attach

- Opportunities for multi-chip hybrid integration

- Silicon photonics

- $\circ$  III-V compound semiconductors

- $\circ$   $\;$  Thin-film Lithium Niobate, BTO, other platforms

SiEPICfab – Canada's silicon photonics fabrication consortium

EPIC

# SiEPIC – the Silicon Electronic Photonic Integrated Circuits program

#### **Education – SiEPIC**

Since 2008, we have offered courses with designfabricate-test cycles (workshop format):

- SiEPIC-Passives, SiEPIC-Actives •

- 28 SiEPIC workshops so far •

- Workshops have trained 596 students, from • 50 universities (total of 123 groups), from 32 companies or gov't labs

- Delivered by universities and CMC

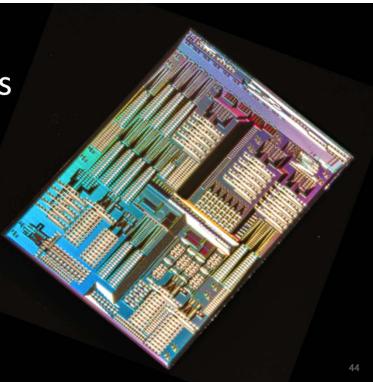

#### Fabrication – SiEPICfab

Canada's silicon photonics fabrication consortium

- University researchers, government funding

- Partners offering design tools, fabrication and MPW runs, test, packaging, incubation

- End users with applications

- Accelerate silicon photonics development cycle

Using Electron Beam

#### SiEPICfab Process Development EcoSystem

# **UBC Nanofabrication Facility - Silicon Photonics Infrastructure**

- Electron beam lithography cleanroom (\$0.6M)

- Electron beam lithography, Jeol JBX-8100FS (\$3M) operational 0 since 2018

- 100 kV, 125 MHz, Write-field up to 1 mm x 1 mm 0

- 0 Overlay accuracy +/- 20 nm (< 10 nm typical)

- Small pieces to full wafers up to 200 mm 0

- New cleanroom, Nanofab (\$5M) opened 2020; new equipment:

- AJA sputtering / evaporator 2018 0

- Contact mask aligner 2018 0

- Heidelberg MLA150 Maskless Lithography System 2020 0

- Inductively Coupled Plasma (ICP) etcher, dedicated for Silicon -0 2020

- Vanguard 3D Laser Printer for Photonic Wire Bonds 2020 0

- Tresky Die Bonder and Component Placer, TPT Automatic Wire 0 bonder - 2021

- New RIE for ashing and NbTiN 2022 0

- Planning for a new PECVD for oxide and nitride 0

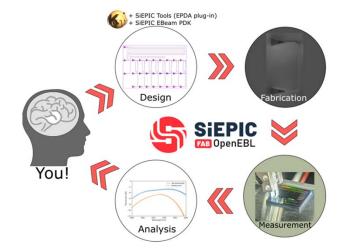

#### free educational fabrication & test SiEPICfab OpenEBL

- Free fabrication and testing through the OpenEBL program.

- Limited fabrication process, single • etch EBL layer, no metals or other process steps.

- Testing at UBC, and designers will be provided with results, will not receive chips.

- Primary purpose is to act as an • educational platform, but may be useful for testing new designs.

- More information on OpenEBL can be found here: https://siepic.ca/openebl/

#### Contributors to the Photonic Wire Bond MPW project

- Lukas Chrostowski, Professor, SiEPICfab PI/UBC/Dream Photonics

- Serge Khorev, Steve Gou, Project Manager, Project management

- Kashif Awan, Research Associate, UBC: EBeam lithography development

- Matthew Mitchell, Postdoctoral Fellow, Dream Photonics/UBC: Photonic wirebond development, SiP chip fabrication and laser integration

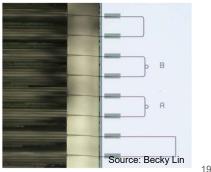

- Becky Lin, MASc student, UBC: Photonic wirebond development and cryogenic experiments

- Shangxuan Yu, MASc student, UBC: PWB Laser integration

- Iman Taghavi, PhD student, UBC: SOA integration, polymer modulators

- Naman Pant, Dream Photonics: Photonic wirebond development

- Alexander Tofini, MASc student, UBC: Simulation and modeling

- Colin Parkyn, coop, UWaterloo: Photonic wirebond development

- Davin Birdi, coop, UBC: Photonic wirebond development

- Sheri Jahan Chowdhury, MASc student: SiP chip fabrication, laser test

- Jaspreet Jhoja, PDK development, SiEPICfab: PDK Development

- Mustafa Hammood, PhD student, UBC/Dream Photonics: PDK Dev

- Sean Lam, MASc student, UBC: PDK Development

- Dias Azhihulov, MASc student, UBC: PDK Development

- Omid Esmaeeli, PhD student, UBC: PDK Development

- · Applied Nanotools: SiP chip fabrication and process development

- CMC Microsystems: Aggregation and invoicing

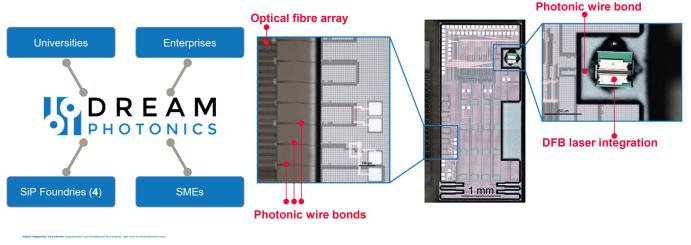

#### Dream Photonics — Building the photonic ecosystem

- Spin-out of UBC utilizing the PWB tool for hybrid integration and packaging

- >10 employees building advanced manufacturing capabilities

- 14 customers exploring PWB technology with Dream Photonics since 2022

Thank you

# Cryo testing – using automated fibre array or photonic wire bonds

| Fixed Coupling via Glued Fibre(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Flexible Coupling via Piezo Stages                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Minmin You, Zude Lin, Xiuyan Li, and Jingquan Liu, "Chip-Scale Silicon Ring<br>Resonators for Cryogenic Temperature Sensing," J. Lightwave Technol. 38, 5768-<br>5773 (2020)         Image: Strate Silicon Ring<br>angle-polished fiber<br>optomechanical<br>cavities<br>cavities<br>glue         Image: Strate Silicon Ring<br>angle-polished fiber<br>optomechanical<br>cavities<br>glue         Image: Silicon Ring<br>angle-polished fiber<br>optomechanical<br>cavities<br>glue         Image: Silicon Ring<br>angle-polished fiber<br>optomechanical<br>cavities<br>glue         Image: Silicon Ring<br>angle-polished fiber<br>optomechanical<br>cavities<br>glue         Image: Silicon Ring<br>Ring Silicon Ring<br>Biologic All Silicon Ring<br>Ring Ring Silicon Ring<br>Ring Ring Ring Ring Ring<br>Ring Ring Ring Ring Ring Ring Ring<br>Ring Ring Ring Ring Ring Ring Ring Ring | H. Gevorgyan, A. Khilo, D. Van Orden, D. Onural, B. Yin, M. T. Wade, V. M. Stojanović, and<br>M. A. Popović, "Cryo-Compatible, Silicon Spoked-Ring Modulator in a 45mm CMOS<br>Platform for 4k-ko-Rom-Temperature Optical Links," In <i>Optical Fiber Communication</i><br>Conference ( <i>OFC</i> ) 2021 |

| <ul> <li>[+] Compact integration, small footprint, low heat load</li> <li>[+] Low cost</li> <li>[+] No extra electrical/software controls needed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | [+] Measure multiple devices at cryogenic temperature<br>[+] Reuse chip                                                                                                                                                                                                                                   |

| <ul> <li>[-] Require individual active alignment during assembling</li> <li>[-] Prone to breakage from thermal mechanical stress</li> <li>[-] Low optical bandwidth, high insertion loss</li> <li>[-] Spectral shift during cooldown</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>[-] High cost</li> <li>[-] Require additional electrical and software controls</li> <li>[-] Misalignments during cooldown due to thermal<br/>induced movement cause signal lost</li> <li>[-] Require large footprint</li> </ul>                                                                  |

### Photonic wire bonding FAQs

- What is the maximum power the PWB can tolerate?

- Vanguard has shown no degradation for a fiber-to-fiber PWB up to 29 dBm at 1540 nm

- Electrical wire bonding or photonic wire bonding first?

- Depends on the assembly, but the recommendation is that electrical wire bonding should be performed last.

- Are the PWBs polarization maintaining?

- Yes the PWBs we are currently using have rectangular or elliptical cross-sections.

- You can even build polarization rotators/splitters out of them

- Can PWBs be operated at visible wavelengths

- Samples have been fabricated, waiting for test results

- 780 nm similar insertion losses

- How mechanically stable are the PWBs?

- Vibration tests have shown no difference in reliability between clad and un-clad PWBs.

- o Mass and forces are so low on these structures which makes them resilient

- Does oxide need to be removed for PWB?

- For surface tapers, yes, but not for edge coupler interfaces.

54

#### Photonic wire bonding FAQs

- Do you have any data on the reflections caused by the PWBs?

- -30 dB return loss

- How long does it take to write a single PWB?

- Depends on the size, but on the order of 30 120 seconds

- Is there any data on PWB performance in cryogenic conditions?

- Ref: Becky Lin, arXiv:2307.07496

- Is there any long term reliability data on the PWBs?

- Demonstrated for waveguide-to-waveguide bonds on the same SiP chip:

- Telcordia Ref. 3.3.2.2: 225 cycles of -40 °C to +85 °C (> 200 h)

- Telcordia Ref. 3.3.2.3: 85°C / 85% humidity, 3500 h

55

# Photonic wire bonding FAQs

- What are the main sources of loss in the PWB?

- Under investigation.

- Bend loss due to radiation

- negligible for bends with radius > 100 μm

- Roughness of PWB (it is written layer by layer)

- Placement accuracy (~30 nm)

- PWB interface design versus what is fabricated

- Mode and index matching

- How far apart can components be for PWB, and what is the alignment tolerance?

- $\circ~$  The writefield is ~ 350  $\mu m$  x 350  $\mu m,$  which limits maximum distance between components.

- Absolute maximum vertical offset between components is 250 µm.

However, for a low loss bond, alignment accuracy of components should be kept <30 µm as a general rule.</li>

# Assembly Design Kit

- Assembly Design Kit

- Documentation on building assemblies, rules for chip designers, GDS cells for fiber/laser coupling

- Some considerations

- $\circ$  Sample height: limit of 250  $\mu m$  above the PWB

- Order of operation of electrical wire bonding (EWB), and photonic wire bonding (PWB) + cladding:

- $\blacksquare EWB \rightarrow PWB \rightarrow PWB Cladding$

- $PWB \rightarrow EWB \rightarrow PWB$  Cladding

- $\blacksquare PWB \rightarrow PWB Cladding \rightarrow EWB$

- Component misalignment < 30 μm</li>

Source: Becky Lin