# **Acronyms**

- ASIC American Semiconductor Innovation Coalition

- COE Coalition of Excellence

- · **IDM** Integrated Device Manufacturer

- NAPMP National Advanced Packaging Manufacturing Program

- NSTC National Semiconductor Technology Center

- OSAT Outsourced Semiconductor Assembly and Test

- UFC University Focus Center

ASIC | Recent Activations

### **Contents**

- **Problem Statement** very limited US self-sufficiency in Semiconductor Packaging

- Solution: CHIPS Act \$52B over 5 years for Semiconductor and Packaging R&D

- · ASIC American Semiconductor Innovation Coalition

- NAPMP Proposed ASIC Framework for the National Advanced Packaging Manufacturing Program

ASIC | Recent Activations

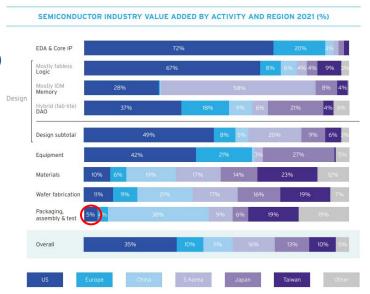

# The US Houses only ~5% of the Packaging Industry (by Value Added)

Negative Implication:

• Surety of Supply

Packaging Assembly & Test is the weakest link in the Supply Chain for the United States.

Source: SIA, State of the Industry report, Nov'22

SIC | www.asicoalition.org

4

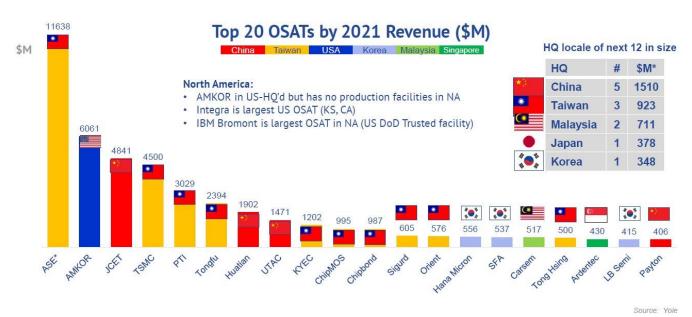

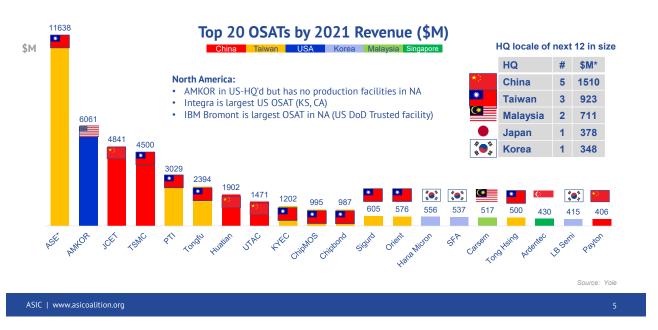

# China & Taiwan Dominate the OSAT Landscape

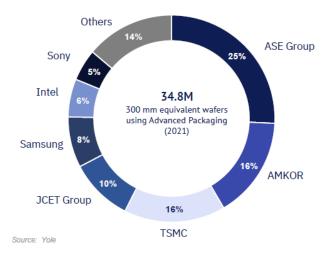

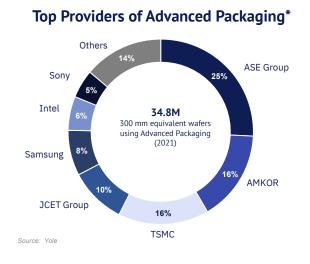

# 6 Companies Package 80% of wafers using Advanced Packaging

# Top Providers of Advanced Packaging\*

ASIC | www.asicoalition.org

| Company    | HQ          | Advanced<br>Packaging Main<br>Factory Location(s) |  |  |  |

|------------|-------------|---------------------------------------------------|--|--|--|

| ASE Group  |             |                                                   |  |  |  |

| AMKOR      | 11.         | <b>(6)</b>                                        |  |  |  |

| TSMC       |             | •                                                 |  |  |  |

| JCET Group | *3          | *                                                 |  |  |  |

| Samsung    | <b>*•</b> * |                                                   |  |  |  |

| Intel      | 14.         | Vietnam Malaysia                                  |  |  |  |

|            |             |                                                   |  |  |  |

Advanced Packaging includes: all flip chip, all wafer level packaging technologies, and all [2.x and 3D technologies.

ASIC | www.asicoalition.org 6

# **China & Taiwan Dominate the OSAT Landscape**

# 6 Companies Package 80% of wafers using Advanced Packaging

**Advanced Packaging** includes: all flip chip, all wafer level packaging technologies, and all 2.x and 3D technologies.

ASIC | www.asicoalition.org

6

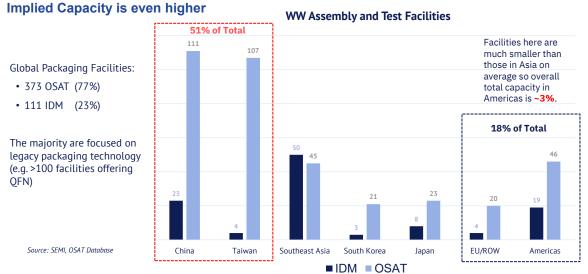

# >50% of the World's Packaging Facilities are in China + Taiwan

ASIC | www.asicoalition.org

7

# **OSAT Manufacturing in US has two Major Barriers to Entry**

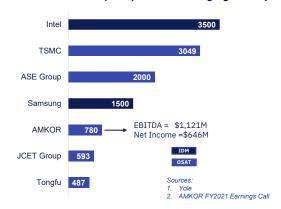

#### Estimated 2021 CapEx spend for Packaging Activity<sup>1</sup>

... and this with all major manufacturing operations being in Asia.

Financial sustainability is a problem even if you have the initial CAPEX to launch.

ASIC | www.asicoalition.org

8

# **CHIPS Act Funding Status**

# Proposed \$52B in appropriations

Several cross-NIST, DOC, Interagency and White House Teams are developing plans for implementation when funds are appropriated for the implementation of the CHIPS Act R&D Programs

|      |               | Proposed appropri                           |         |      | priati | ons  |      |

|------|---------------|---------------------------------------------|---------|------|--------|------|------|

|      |               | CHIPS Act                                   | FY 2022 | 2023 | 2024   | 2025 | 2026 |

|      | Section       | CHIPS ACT                                   | \$ B    | \$ B | \$ B   | \$ B | \$ B |

|      | 9902          | Semiconductor incentives                    |         |      |        |      |      |

|      | 9902          | Incentives Program                          | 19      | 5    | 5      | 5    | 5    |

|      | 9906          | Advanced microelectronics R & D             |         |      |        |      |      |

| ASIC | 9906 <b>c</b> | National Semiconductor Technology Center    | 2       |      |        |      |      |

| ASIC | 9906 <b>d</b> | Nat. Advanced Packaging Manufacturing Prog. | 2.5     | 2    | 1.3    | 1.1  | 1.6  |

|      | 9906 <b>e</b> | Microelectronics Research at NIST           | 0.5     |      |        |      |      |

|      | 9906 <b>f</b> | Manufacturing USA Institute                 | 0.5     |      |        |      |      |

Source: Robert Rudnitsky, NIST

American Semiconductor Innovation Coalition | 2022

9

# ASIC Notional Structure of Authorized Programs in CHIPS Act

## **American Semiconductor Innovation Coalition (ASIC)**

#### Who we are:

The American Semiconductor Innovation Coalition (ASIC) represents more than 175 businesses, startups, universities, national labs, and nonprofits dedicated to bringing the best research and development to The National Semiconductor Technology Center (NSTC) and The National Advanced Packaging Manufacturing Program (NAPMP).

#### Our approach:

#### **Broad Representation**

Robust governance model with diverse representation from industry, government, academia, national labs and small businesses to define and implement an ambitious technical agenda and roadmap

#### Coalitions of Excellence

Network of core research centers across the U.S. with key infrastructure to execute research agenda, facilitating technology development, maturation and translation from 'lab to fab'

# Investment Fund and Start-up Support

Funding opportunities for new ventures, in addition to support for early-stage start-ups; leveraging resources across Coalitions of Excellence to provide start-ups with access to expertise, facilities and equipment

#### Education & Workforce Development

A nation-wide program to develop and rapidly adopt educational content, investing in and supporting equitable education and training programs and facilities accessible to a broad range of institutions

ASIC | www.asicoalition.org

11

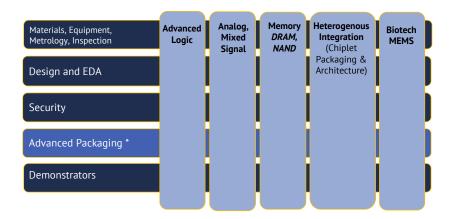

#### **ASIC Technical Team**

#### 300+ participants across 10 Work Groups

\* Denotes NSTC, NAPMP scope

ASIC | www.asicoalition.org

12

# **Advanced Packaging Workstream Sub-Team Organization**

#### 9 horizontal teams and 1 cross-cutting vertical team

ASIC | www.asicoalition.org ASIC CONFIDENTIAL 13

# **ASIC Advanced Packaging Team**

**Who are we?** 138 members from across 79 entities

| 19 Universities<br>37 members                                                                                                                                   |                                                                                                               | 48 Com<br>87 mer                                                                                             |                                                                                                                  |                                                                                                                     | 3 Industry Assoc<br>3 members                                    | 2 MIIs<br>4 members                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------|

| BU U Delaware Cornell U Illinois GaTech U Michigan MIT U Minnesota Penn State U Puerto Rico Princeton U Vermont Purdue UCLA RPI UIUC SUNY USC(ISI) U Binghamton | 3D Glass<br>ADI<br>Advantest<br>AMAT<br>AMID<br>Analog<br>Photonics<br>ASPDL<br>AT&S<br>Atomica<br>Canon Nano | DECA Dupont FormFactor GE Research Global Foundries Green Source Hyperion i3 Micro IBM Integra Jabil Resonac | JSR Micro<br>Keysight<br>KLA<br>LAM<br>Marvell<br>Mercury<br>Mosaic<br>NANTERO<br>nepes<br>NGC<br>Nhanced<br>WDC | Novami<br>NXP<br>Siemens<br>Skywater<br>Sunray<br>TEL<br>Teledyne<br>TI<br>TTTM<br>UI Corp<br>ULVAC<br>Veeco<br>WDC | iNEMI IPC SEMI  3 Analysts 3 members TechCet TechSearch Yole Dev | AIM Photonics NextFlex  3 National Labs 3 members ANL CEA-LETI Fraunhofer |

ASIC | www.asicoalition.org

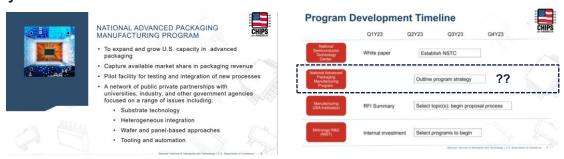

#### **NAPMP Direction**

NIST/DOC direction for the NAPMP has been sparse despite \$2.5B allocated in first year

Nevertheless, the ASIC Advanced Packaging Teams have been active in planning

ASIC | www.asicoalition.org

# **ASIC NAPMP Objectives**

- Encourage and support advanced research to create totally new technologies, designs and products.

- Accelerate technology development

- Transfer new technology to US commercial production

- Support workforce development

- Maintain close links with the NSTC

ASIC | www.asicoalition.org

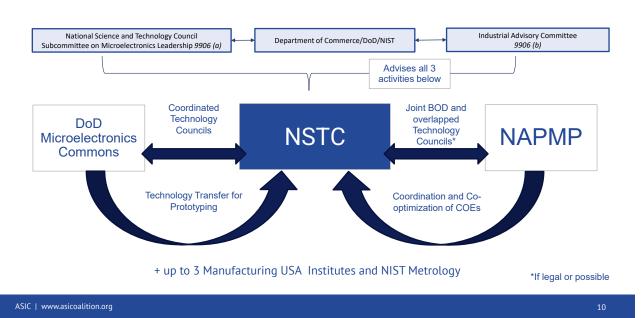

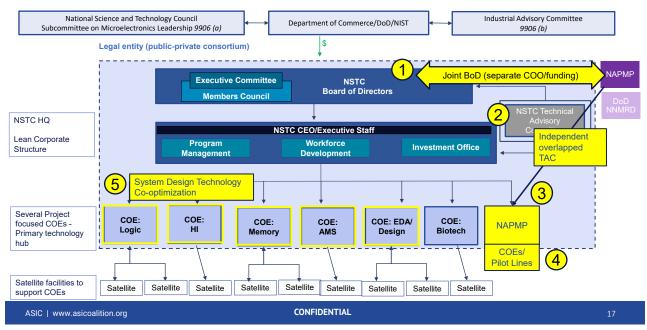

# **NSTC** proposed structure – **NAPMP** Connection

# **NSTC/NAPMP** Relationship

- To avoid duplicate overhead costs and to ensure strategic alignment, we recommend that the NSTC and the NAPMP share:

- Board of Directors

- Workforce Development

。 CEO

- Support Staff where possible

- To ensure appropriate governance and funding, we recommend that the NSTC and NAPMP have separate:

- COEs

Budget / Financial Management

。 COO

- Program Management

- Technical Advisory Committees

ASIC | www.asicoalition.org

18

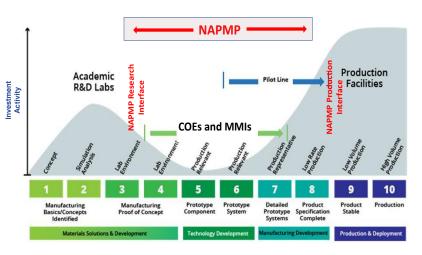

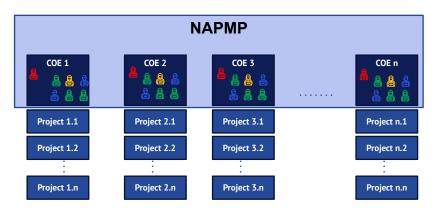

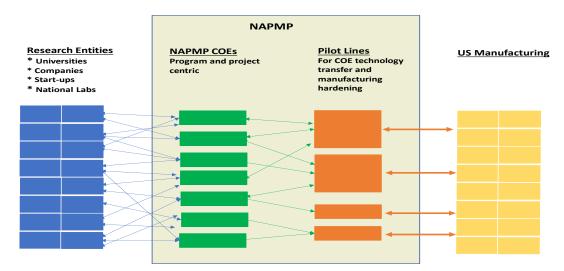

# **Proposed NAPMP COE Structure**

As a "Manufacturing Program", we assume the NAPMP COEs will be program focused and will not typically have their own facilities

#### Major tasks would be;

- Research interface

- · Road mapping

- Program selection, funding, objectives, monitoring to accelerate technology development

- Transfer of technology to pilot lines

- Each COE has a specific technology theme

- COE should have industry/university inputs, along with NIST inputs, into decision making

ASIC | www.asicoalition.org

CONFIDENTIAL

10

# **Conceptual Schematic of the NAPMP**

SIC | www.asicoalition.org

20

# Major Markets Enabled By Advanced Packaging

- High performance computing (including AI) with reduced energy consumption (3DHI, Co-Packaged Optics)

- Memory centric computing (3DHI)

- Defense, 6G, autonomous driving (>60GHz packaging)

- EVs, renewable energy (high voltage/power packaging)

- Data communications, AR headsets, autonomous driving LIDAR (3DHI, Co-Packed Optics)

- Wearable medical devices (MEMS, low power, size, flexible electronics)

- · Aerospace and Defense (all of the above)

ASIC | www.asicoalition.org

2

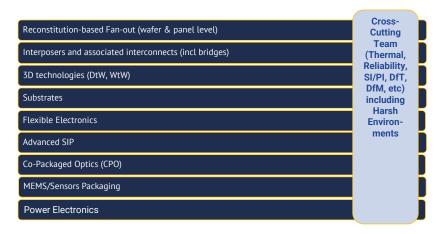

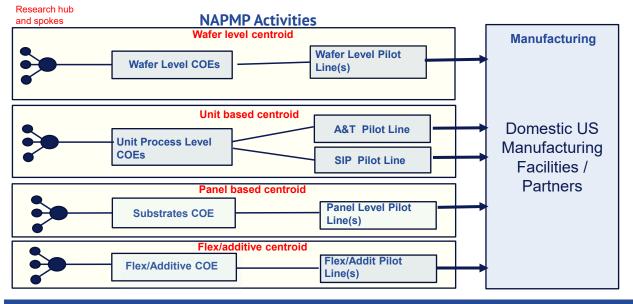

## **NAPMP Coalitions of Excellence (COEs)**

The COEs would focus on accelerating technology development in the NAPMP, each with a particular technology theme. Ten proposed:

- 3D heterogeneous integration

- Copackaged optics (CPO)

- Advanced SIP

- High voltage/high power

- FO-WLP (reconstituted)

- Interposers/Bridges

- Substrates

- MEMS

- Flexible Hybrid & Additive

- Cross cutting (eg thermal, reliability, DFM, etc)

Each COE would have sub-COEs to drive subsets of the technology.

Example: 3D HI

- Co-design EDA for design and test

- Hybrid bonding *[example Projects]*

- Bonding down to 2um bond pitch plus improved wafer finishing

- o Alignment to 100nm

- Higher throughput tools with die speed binning capability

- New materials to reduce anneal temperature

- Data management for increased yield and traceability

- · Thermal dissipation

- Below surface metrology

- Reliability

ASIC | www.asicoalition.org

22

# **Research – University Focus Centers**

- Research and innovation is a great strength for the United States. Large research universities are very hard to replicate, and we need to leverage this advantage we have.

- Each NAPMP COE should be linked to a lead university with expertise in its technology and other universities in a hub and spoke structure.

- The NAPMP should support both capital and operating cost for funded projects.

- The COE and the universities should collaborate on road mapping and areas for research, with some funding for theme-based undirected research

ASIC | www.asicoalition.org

2

# **Proposed COE/Pilot Line Approach**

ASIC | www.asicoalition.org

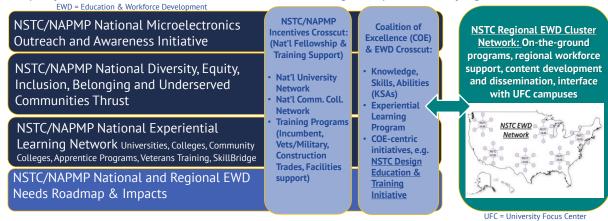

## **NSTC/NAPMP EWD – Key Components & Program Strategy**

Developed by 80+ Person EWD Team from 65 ASIC Universities, Comm. Colleges, Companies & Industry Orgs

- ASIC's EWD Team is assembling an adaptive National EWD Platform to engage NSTC COE's, industry, academia and WFD organizations from across the U.S. to expand and elevate the national microelectronics workforce

- ASIC's National EWD Platform will enable broad national participation, scale and sustain successful EWD programs, promote

DEIB, and engage underserved communities across the U.S. in semiconductor careers.

ASIC | www.asicoalition.org

# **Proposed NAPMP Success Metrics**

The NAPMP needs to monitor a broad set of success metrics, both leading and trailing, covering four areas:

- Operations

- Technical

- Economic

- Workforce Development

| Area       | ASIC Proposed NAPMP Metrics                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                              |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Operations | #of NAPMP projects taken to production in USA     #of members and dues paid     #of projects delivered on schedule     #of projects transfer to manufacturing                                                                                                                 | Budget control     # of research partnerships (academic and commercial)     Progress towards industry self sufficiency for the NAPMP     Assess performance of each NAPMP COE                                                                                                |  |  |

| Technical  | Roadmap acceleration versus prior expectations     US technical leadership     # of technologies/processes/products transferred to     manufacturing     Reduced environmental footprint for packaging technologies                                                           | # of breakthrough challenges supported by NAPMP developed technologies     # of projects terminated for technical reasons     # of patents and license revenue     # of peer reviewed papers and conference presentations                                                    |  |  |

| Economic   | US production market share in semi packaging (advanced and mature)  + of new jobs created in US packaging facilities Growth of new industries supported by the NAPMP (eg EV, medical etc)  Growth of US based packaging foundry                                               | # of start-up companies supported by NAPMP     # of packaging related start-ups reaching successful exit     National security support     # of projects terminated for market reasons     Improved supply chain resilience (less dependence on Taiwan)                      |  |  |

| Workforce  | # of students in training versus goals (AA, BS, MS, PhD)     % minority and retrained students (eg military)     # of students hired by semiconductor packaging industry     # of semi packaging centric locations, courses and programs     Geographic diversity of training | <ul> <li>% students graduating in 2 years (CC) and 4 years (BS)</li> <li># students hired by semi-industry</li> <li>Number of CCs, colleges, and universities offering courses.</li> <li># of student internships (at multiple levels: 2-year, 4-year, post-grad)</li> </ul> |  |  |

ASIC | www.asicoalition.org

## **Summary**

- The ASIC NAPMP team has developed an organization and structure for the NAPMP built around:

- Ten Coalitions of Excellence for accelerated technology development

- Five Pilot Lines for economic and sustainable manufacturing hardening

- University Focus Centers leading the university research efforts

- The NAPMP objectives are:

- Support research activities in advanced packaging

- Accelerate technology development

- o Develop and harden economically and sustainable manufacturable processes

- Transfer technology for manufacture to support multiple new market opportunities

- The NAPMP will collaborate with multiple organization including the NSTC, companies, universities and other government programs

ASIC | www.asicoalition.org

#### To Learn more about ASIC

- → Website: <a href="https://asicoalition.org/about">https://asicoalition.org/about</a>

- → Twitter: <a href="https://twitter.com/asicoalition">https://twitter.com/asicoalition</a>

- → Linkedin: https://www.linkedin.com/company/american-semiconductor-innovation-coalition/