### SiP and Module

### (Heterogeneous Integration Roadmap (HIR) Annual Meeting 2023, Milpitas)

**Rolf Aschenbrenner** is deputy director at Fraunhofer IZM and head of department System Integration and Interconnection Technologies. He is IEEE Fellow and has had long-term activities for IEEE.

**Dr. Klaus Pressel** joined Infineon in 2001, where he is now responsible for innovations in assembly and packaging technology. Klaus also represents Infineon in various European research programs, global technical committees and international conferences.

**Erik Jung** is with the Fraunhofer IZM, serving as Business Developer for Advanced System Integration Solutions. He is Member of IEEE and has long standing activities within the IEEE community

Supported among others by: Harrison Chang (ASE), Hannes Stahr (AT&S), Key Chung (SPIL), Peter Machiels (Philips), Thomas Zerna (TU Dresden), Hugo Pristauz (BESI)

**Definitions and Classification**

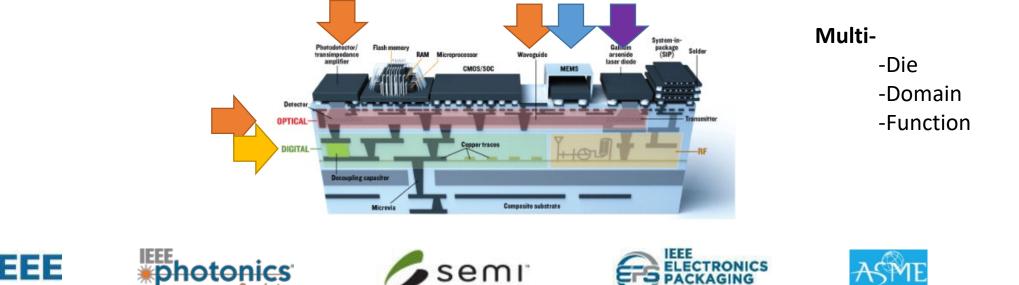

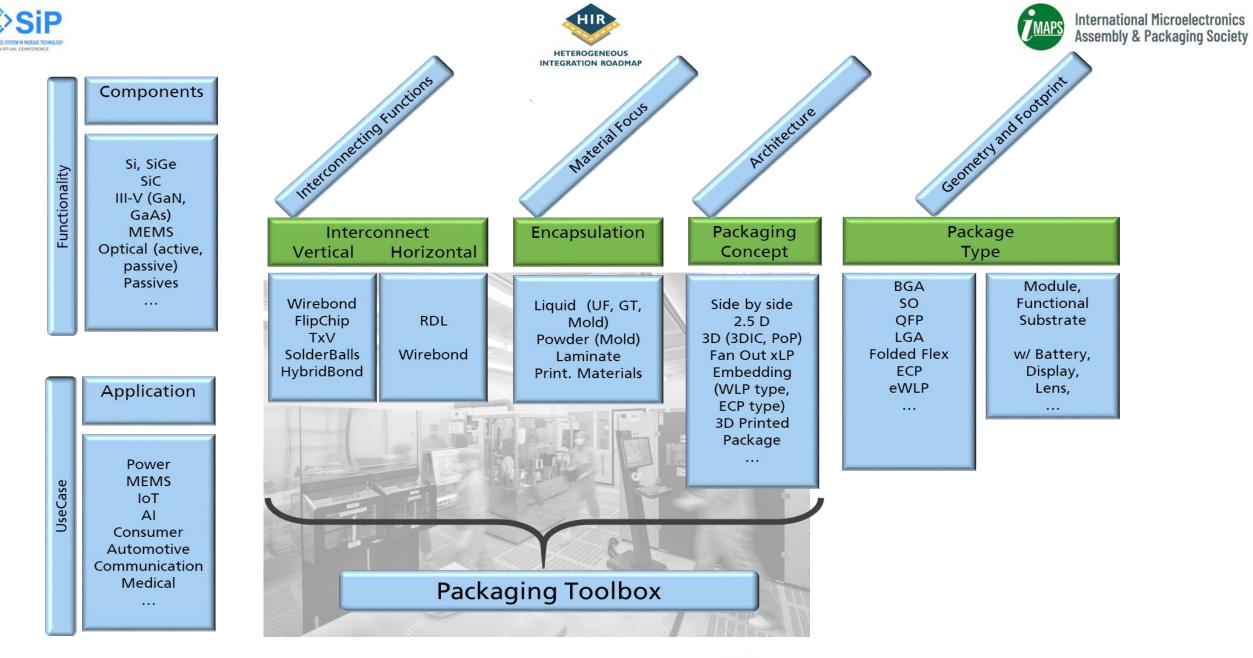

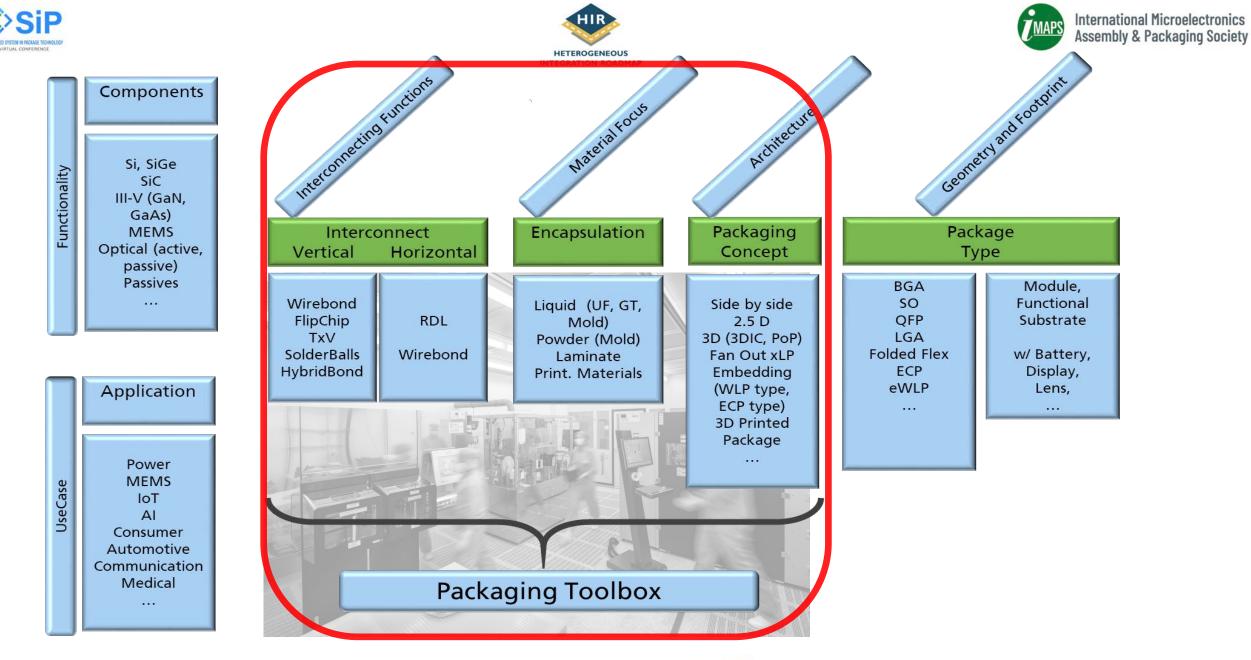

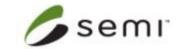

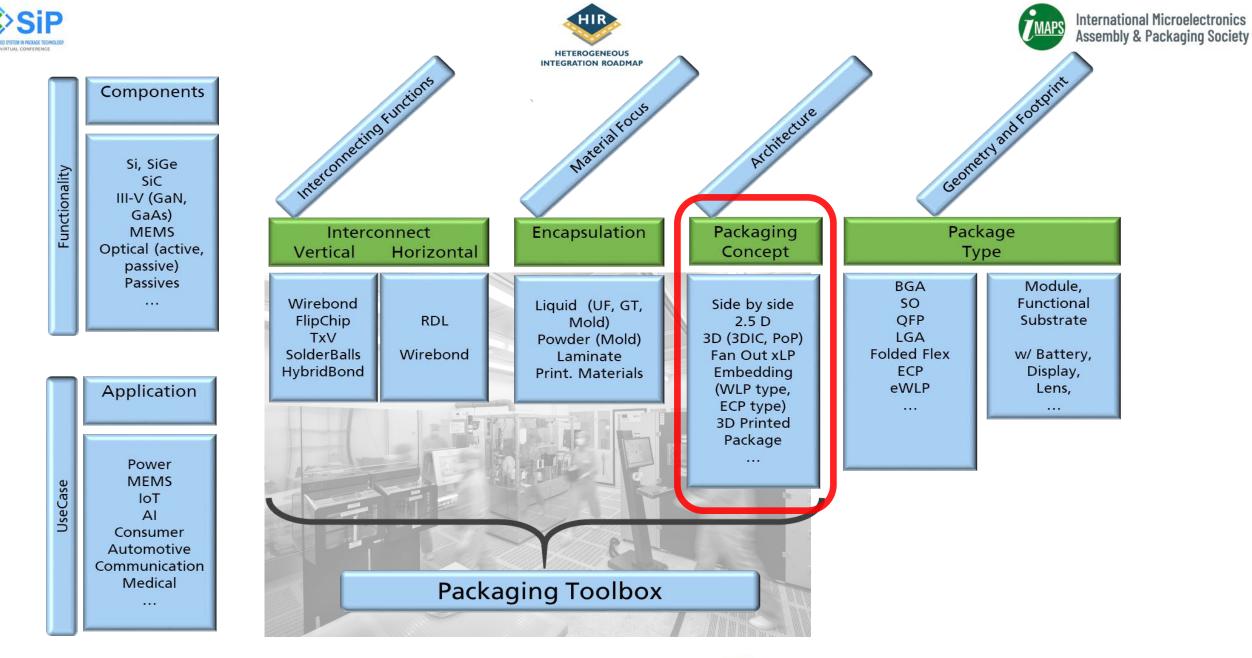

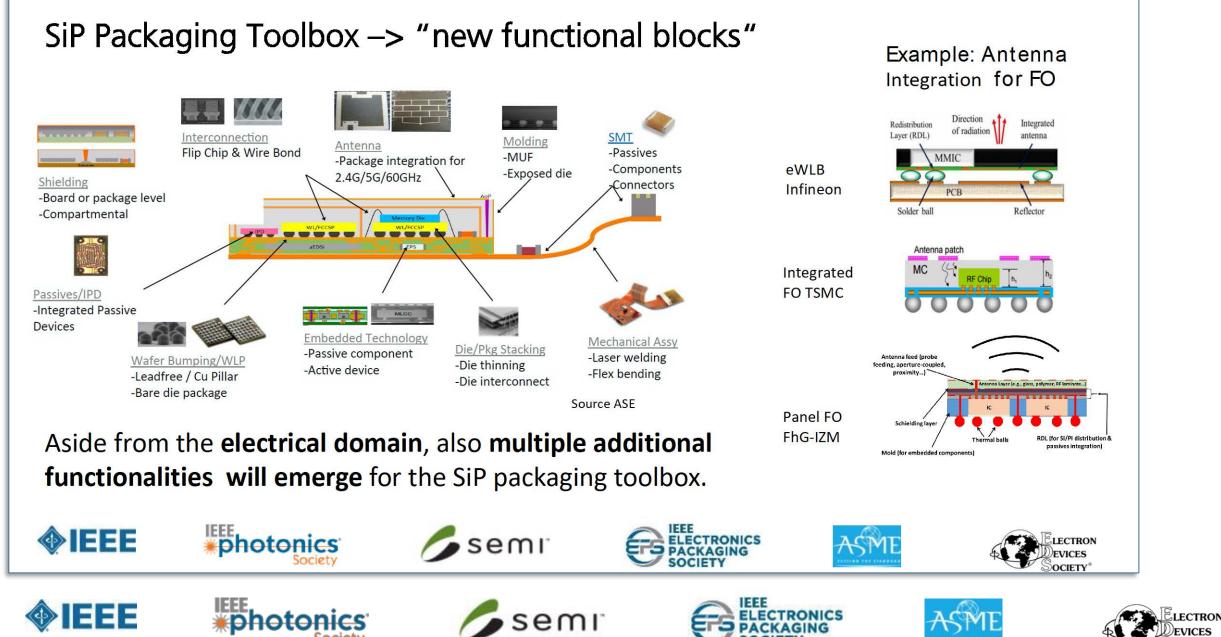

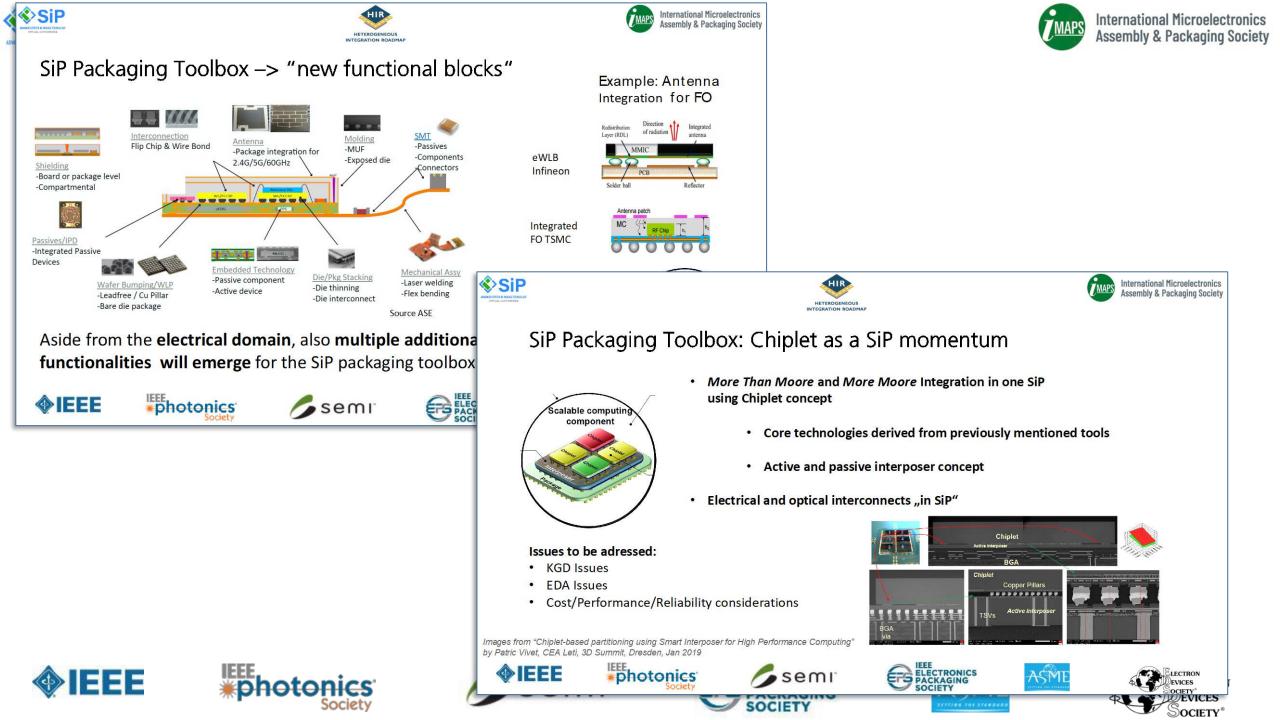

Toolbox for SiP

Challenges

# **Definitions and Classification**

Toolbox for SiP

Challenges

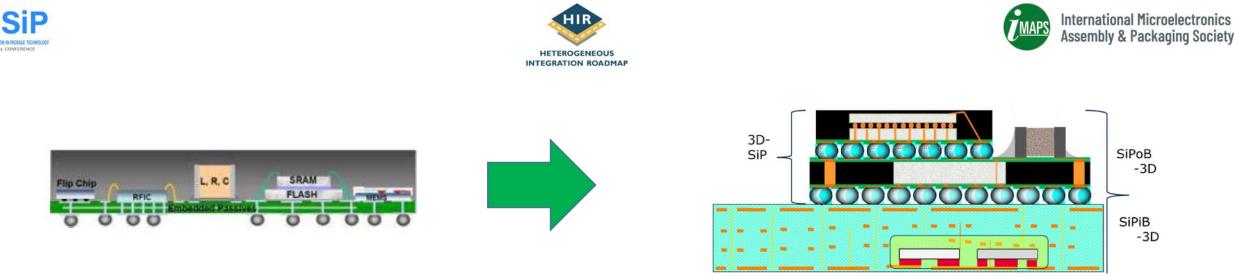

#### **Definition of SiP**

Electron Devices Society®

"SiP, or System-in-Package, refers to a package (such as SO, QFP, BGA, CSP,LGA) that has multiple die (Si, GaAs, SiGe, and or SOI) plus optional passives integrated together. The package is typically surface mounted to the main board."

**Definitions and Classification**

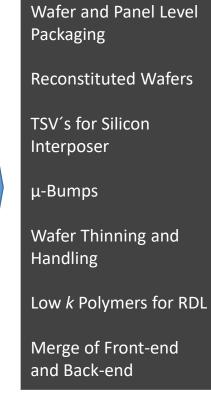

# **Toolbox for SiP**

Challenges

### SiP Packaging Toolbox: Interconnect

#### **Evolution of standard interconnect**

- Wirebond and stacked wirebonds incl. copper wire

- Flip Chips and stacked flip chips (w/ TSV)

- Package on Package (PoP) bump bonding

#### Challenges

- More IO/area, size of microbumps

- Thin chips for thinner stacks

- Warp and I/O arrangement for More than Moore SiP

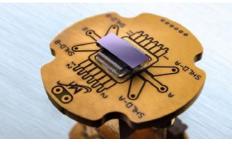

#### New: Embedding Technology – Interconnect by Electroplating

- Embedding of thin active chips into the dielectric layers

- Embedding of passive components together with chips

- Embedding of SMD components for low volume and SME's

Challenges:

- Remaining dielectric thickness decreasing

- Lines/spaces and via otin @ HDI substrates, by shrinking the chip pitch

- Multi material challenge (Si, dielectric, EMC, underfill, die attach ...)

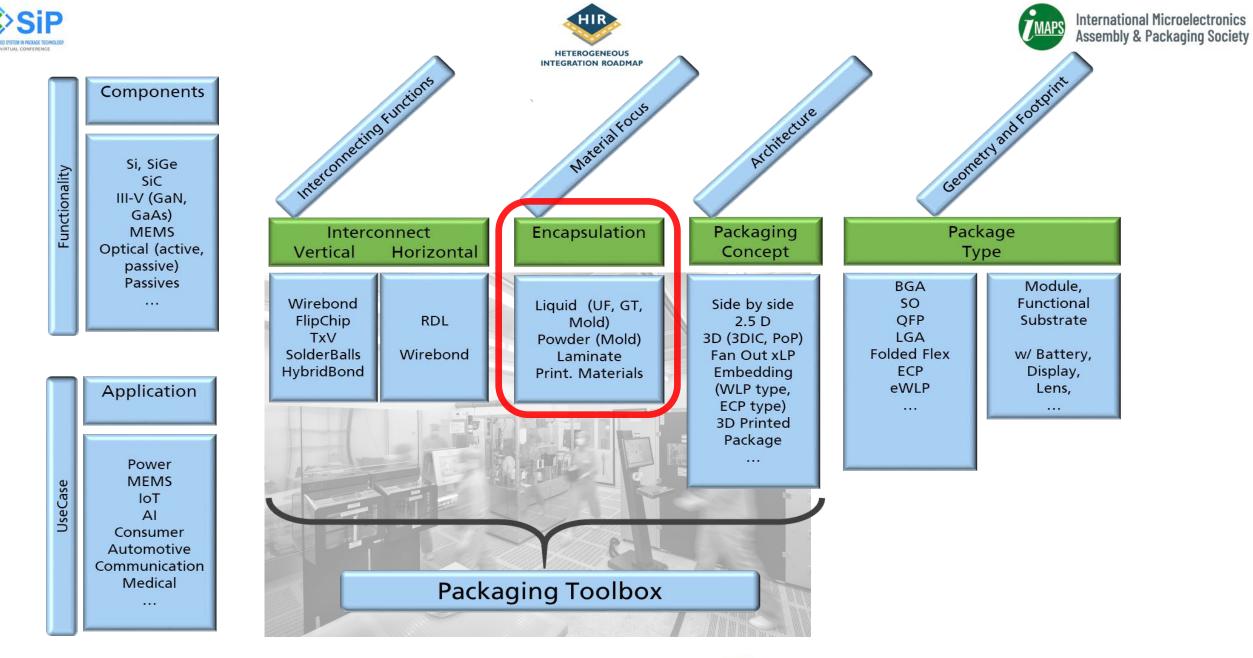

### SiP Packaging Toolbox: Encapsulation

#### Workhorses:

Molding (Pellet)

Glob Top (Dispense)

UnderFill (Dispense)

#### Established:

Molding (Liquid, Compression) Glob Top (Jet and Print) UnderFill (Jet)

#### To Come:

Lamination for thin/flat assemblies

3D Additive as "Structurally Integrated"

Material innovations, process innovations, conceptual innovations drive these advancements

Images: KCC, HybridCH, Finetech, Polymer Innovations, Neotech

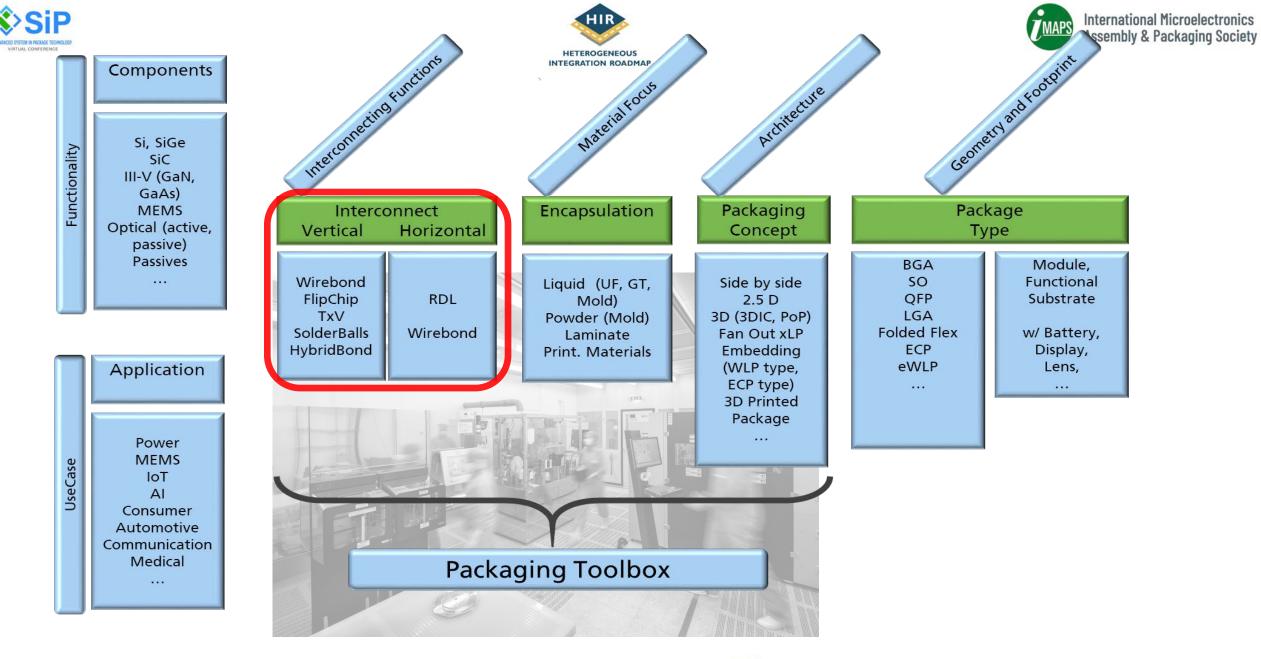

#### SiP Packaging Toolbox

\*photonics

EEE

OCIETY

CTRONICS

|                              | INTEGRATION ROADMAP        |                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |  |  |  |  |  |

|------------------------------|----------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|--|--|

| Concept                      | Material                   | Interconnection                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |  |  |  |  |  |

| Side by Side                 | РСВ                        | Solder<br>Adhesive<br>Wire bond     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |  |  |  |  |  |

|                              | Flex<br>Silicon            | Solder<br>Adhesive<br>Wire bond     | <u>Ann Transman Tambi</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |  |  |  |  |  |

| Stacked / Folded             | РСВ                        | Solder<br>Adhesive<br>Wire bond     | 00000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |  |  |  |  |  |

|                              | Flex                       | Solder<br>Adhesive                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | New Processes |  |  |  |  |  |

|                              | Silicon                    | Solder<br>Wire bond                 | Implementaria     PRAMINA       Implementaria     Provide a state       Implementaria     Provide a state | Pro           |  |  |  |  |  |

| Embedding                    | РСВ                        | Solder<br>Electroplated             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | New           |  |  |  |  |  |

|                              | Flex                       | Solder<br>Adhesive<br>Electroplated |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |  |  |  |  |  |

|                              | Thin film<br>(Wafer Level) | Electroplated                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |  |  |  |  |  |

| Fan Out<br>Wafer/Panel Level | Mold compound              | Solder<br>Adhesive<br>Electroplated |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |  |  |  |  |  |

| Module                       | PCB<br>Flex                | Solder<br>Adhesive<br>Electroplated |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |  |  |  |  |  |

semi

IEEE

SOCIETY

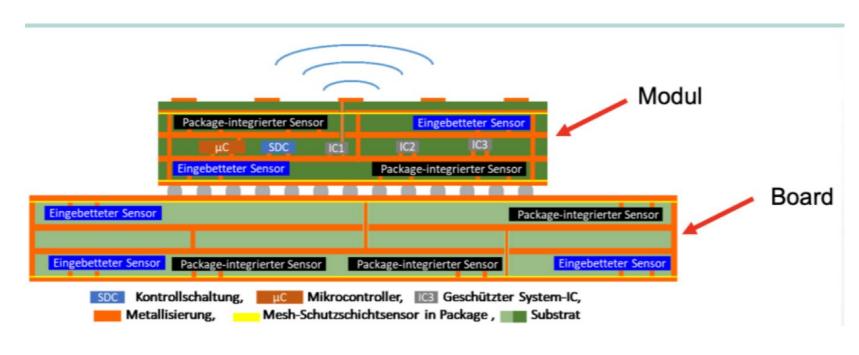

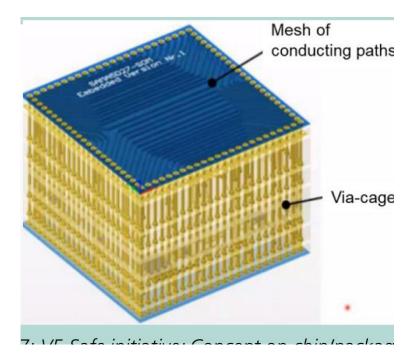

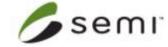

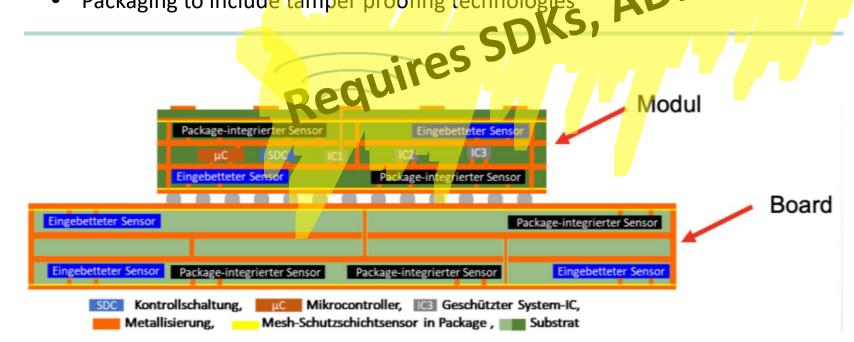

### Chiplets supporting trusted computing concepts

- Critical functionalities can be sourced from trusted entities

- Non critical functionalities can be sourced from redundant suppliers and independently verified

- Integration by advanced packaging done by trusted entities

- Packaging to include tamper proofing technologies

### Chiplets supporting trusted computing concepts

- Critical functionalities can be sourced from trusted entities

- Non critical functionalities can be sourced from redundant suppliers and independently verified

- Integration by advanced packaging done by trusted entities / c 3

- Packaging to include tamper proofing technologies

**Definitions and Classification**

Toolbox for SiP

Challenges

# New/future requirements derived from different application areas as indicators for roadmap targets => New challenges

**RF/THz**

Power

**Autonomous Systems**

loT

Consumer

Wearables

**Quantum Devices**

# **Difficult Challenges for Implementing SiP**

| N ROA | DMAP                                   |                                                                                                                                                                                             |                                                                                                                         | SEM Image of cross-section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Materials                              | <ul> <li>New materials (HF materials)</li> <li>Material interactions</li> <li>Failure modes</li> <li>Thermal mismatch</li> </ul>                                                            |                                                                                                                         | Cross-section of RCC<br>Iseminated system after<br>stress. Crack's in the<br>RCC material form<br>between RDL copper<br>and the chip surface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | Cost                                   | <ul><li>New package platform (FO, embedding)</li><li>Complex Systems</li></ul>                                                                                                              | Link Controller WI-Fi Module<br>Contains 2.4GHz WI-Fi ATWILC2000,<br>crystel, power inductor, and<br>21 L & C discretes | x3.4 mm shielded module variety of components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | Assembly                               | <ul> <li>Technology Diversity (Sensors, antenna, IC's,</li> <li>Pitch, soldered and non-solderd components</li> </ul>                                                                       | passives                                                                                                                | already<br>encopsulated<br>ICs passives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       | Standardization<br>common package type | <ul> <li>Footprint</li> <li>Dimensions</li> <li>Thickness</li> </ul>                                                                                                                        | SIP thru Heterogeneous<br>Integration                                                                                   | tragile territes Odd shape, as connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | Customer<br>Requirements               | <ul> <li>Reliability and application specific</li> <li>Temperature / cooling</li> <li>Performance</li> <li>Pitch, dimensions, thickness</li> </ul>                                          | c requirements                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | Test                                   | <ul> <li>Application specific (incl. mixed s</li> <li>Electrical, mechanical and therma</li> <li>Self testing, incl. BIST</li> </ul>                                                        |                                                                                                                         | System Development Chip Development Package Development Board Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | Co-Design                              | <ul> <li>SiP Requiring a system &lt;-&gt; pack</li> <li>Different libraries in one project</li> <li>Multiple domains with different so</li> <li>Thermal, mechanical and electric</li> </ul> | aling properties                                                                                                        | Balout & System Spec     Chip Layout     Lammarke     FOWLP     Laedframe     PCH       Microsoft     Cadenoc     Cadenoc     Virtusos     Layout     Cadenoc     Cadenoc       Virtusos     Schemato     C     C     C     Cadenoc     Cadenoc       Layout     C     C     C     C     C     Cadenoc       Layout     C     C     C     C     C       Export     Peckage     C     C     C     C       Layout     Die     Foorprint     Peckage     PCE       Layout     Die     Pockage     PCE     Layout       Design Project 1     Data Repo     Design Project 2     Data Repo     Internet, Data Repo       File     File     Cadenoci 1     Data Repo     E     C annet to the seconary |

|       |                                        |                                                                                                                                                                                             |                                                                                                                         | HARTEL ALL ALL ALL ALL ALL ALL ALL ALL ALL A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# **Definitions and Classification**

Toolbox for SiP

Challenges

## SiP and Modules are major directions in future microelectronics

## Managing complexity will be a major challenge:

- Functional increase

- Complex material mix on semiconductor, package and board level

- Reliability caused by new applications (in addition => impact on sustainability)

- Thermal management

- Complex testing

- Co-design over various domains chip, package, board, subsystem, ....

- Cost constraints

Refining quantitative details......Strengthen Cross TWG relations...... Assess new/emerging developments (PIC and Quantum....)

| j – T    | Challenge              | State of the Art                                                                                       | Future Perspective                                                                                      |                                    |                                  |                                                                                          |                                                                                                                             |

|----------|------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| <u> </u> | Application Related    |                                                                                                        |                                                                                                         |                                    |                                  |                                                                                          |                                                                                                                             |

| 1        | Functionality Increase | Single domain functionality                                                                            | Multi domain functionality                                                                              |                                    |                                  |                                                                                          |                                                                                                                             |

| 2        | Non-electric functions |                                                                                                        | Integrated in one flow of value chain creation                                                          |                                    | Cross Cutting Aspects            |                                                                                          |                                                                                                                             |

| 3        | Assembly               | Single technology use                                                                                  | Choice from a technology menu built<br>from a compatible tool box                                       | 11                                 | Test                             | Single-domain testing, sequential test of<br>multiple-domain functions                   | Simultaneous testing of multi-domain<br>features to assess cross influences; testing<br>specifically for target application |

| 4        | Reliability            | Standards derived from "typical<br>applications" and adapted to actual use<br>case<br>Material Related | Novel applications driven by new<br>business models may render current<br>standards obsolete            | 12<br>13                           | EDA assisted<br>CoDesign<br>WEEE | Different, incompatible EDA suites<br>Electronics-only functionalities well<br>addressed | EDA suites with a common referral<br>language and APIs<br>Multi-domain functionalities difficult to<br>address              |

| 5        | Material               | Material evolution driven by integration<br>requirements (e.g. high flow epoxies,<br>CuPd wire)        | Material revolution driving integration,<br>disrupting industries' value chains                         | 14                                 | Standardization                  | Standards in formfactor of individual<br>packages                                        | Platform technology with interface to<br>EDA tools ("VHDL for SiP")                                                         |

| e        | Physics Related        |                                                                                                        | 15                                                                                                      | Security Aspects                   | No built-in security features    | Depending on application, specific                                                       |                                                                                                                             |

| 6        | Thermal<br>Management  | passive and active cooling built after<br>simulation/validation assessment                             | Thermal-Electric and Mechanical Co-<br>Design including the <u>SiP</u> integration site<br>via CAD Tool |                                    |                                  |                                                                                          | security features built into hardware may<br>be needed                                                                      |

|          | •                      |                                                                                                        |                                                                                                         | 16                                 | Cost Reduction                   | Cost challenges are addressed only on one                                                |                                                                                                                             |

| 7        | Reliability            | Empirically derived statistical models                                                                 | Physics of Failure Modeling                                                                             |                                    | level in the value chain         |                                                                                          | synergies surpassing individual levels of<br>value chain                                                                    |

| 8        | Form Factor            | SiP design targeting maximum package<br>efficiency limited by physical geometry                        | SiP design with as-needed efficiency,<br>limited by cross-cutting aspects,                              |                                    | High Attention                   |                                                                                          |                                                                                                                             |

| 9        | Signal Integrity       | Individual design and test                                                                             | interdependencies<br>Building blocks for S.I.                                                           |                                    | Midterm Attention                |                                                                                          |                                                                                                                             |

| 10       | Power requirements     | <50W/cm <sup>3</sup>                                                                                   | 200W/cm <sup>3</sup>                                                                                    | No immediate action needs foreseen |                                  |                                                                                          |                                                                                                                             |

#### HETEROGENEOUS INTEGRATION ROADMAP

# Thank you for your attention!

Special thanks for support to Harrison Chang (ASE), Hannes Stahr (AT&S), Key Chung (SPIL\*), Machiel Peters (Philips), Thomas Zerna (TU Dresden), Hugo Pristauz (BESI), Paul Wesling (IEEE), Andrew Liang, Brandon Marin,

Images are referenced in the HIR – SiP&Module chapter, please see there

sem