## The Roaring 20s - A Renaissance for the Semiconductor Industry

Todd Younkin SRC, President and CEO Todd.Younkin@src.org

## **Special Thanks**

- William Chen, ASE

- Bill Bottoms, 3MTS

- Ravi Mahajan, Intel

- Choong-Un Kim, UT/Arlington

- Ganesh Subbarayan, Purdue

- Carol Handwerker, Purdue

- Amy Marconnet, Purdue

- Justin Weibel, Purdue

- Bahgat Sammakia, SUNY-Binghamton

- Muhannad Bakir, Georgia Tech

- Madhavan Swaminathan, Georgia Tech

- Timothy Fisher, UCLA

- Arijit Raychowdhury, Georgia Tech

- Other CHIRP Center Faculty

- Matthew Johnston, Oregon State

- Subramanian lyer, UCLA

+ Their amazing partners and students

Insufficient Time to Share More

## BLUF

- The Heterogeneous Integration Roadmap (HIR) is both a critical reference and an innovation community.

- Academic research related to HIR is crucial, with fruitful areas in both basic & applied research. This

includes all 23 HIR chapters, plus growing vectors like quantum, additive manufacturing, & biology.

- SRC has significantly grown its long-standing commitment to heterogeneous integration or advanced packaging at universities worldwide. For example, GRC-PKG has grown +867% over last 5 years.

- Academics should familiarize themselves with SRC's "3 Pillars" (or 3 Ps), and then...

- Academics should **submit proposals** to these three solicitations (First two are active, Third is planned):

| Program              | Eligible Performers  | Announced     | Link                                                                    |

|----------------------|----------------------|---------------|-------------------------------------------------------------------------|

| JUMP 2.0             | U.S. (DARPA)         | Dec. 21, 2021 | https://www.darpa.mil/news-events/2021-12-22                            |

| NSF REU Program*     | U.S. (NSF)           | Jan. 26, 2022 | https://www.nsf.gov/news/news_summ.jsp?cntn_id=304304&org=ENG&from=news |

| GRC, Packaging (PKG) | U.S. & International | Q2, 2022      | https://www.src.org/compete/                                            |

SRC is pursuing CHIPS ACT funding to revitalize and modernize our mission, aligned to the 3 Ps. Heterogeneous integration is priority #1 for SRC and its members.

\*Administered by NSF. Do not work with SRC or SRC member companies as it is a conflict of interest.

JRC

## The Future of Semiconductors Is Bright

- I started at Intel in 2001, excited about nanotechnology and Intel's race to the atomic length scale. It did not disappoint.

- Recently, the talent pipeline has started to dry up, significantly. The student population is not receptive to the "2D scaling forever" story. That narrative is not finding a way into their hearts and minds!

- Together, we must seek a new narrative. One that helps students realize we have hard yet interesting problems that can't be solved without them.

- All can see the \$2T+ generational opportunities in hyperscaled computing, artificial intelligence, 5/6G+, autonomous vehicles, and quantum. We know these emerging frontiers will change the world around us!

- Yet, collectively, we must apply disciplined imagination. Microelectronics is not static! The future we imagine rests on continued, cost-effective, and innovative **breakthroughs in hardware**. Materials, integration, packaging, design, architecture, and security are all critical elements for success.

There is a bright future. Fascinating opportunities for the next 20 - 30 years, the kind you can build a career on as a young scientist or engineer.

JRC

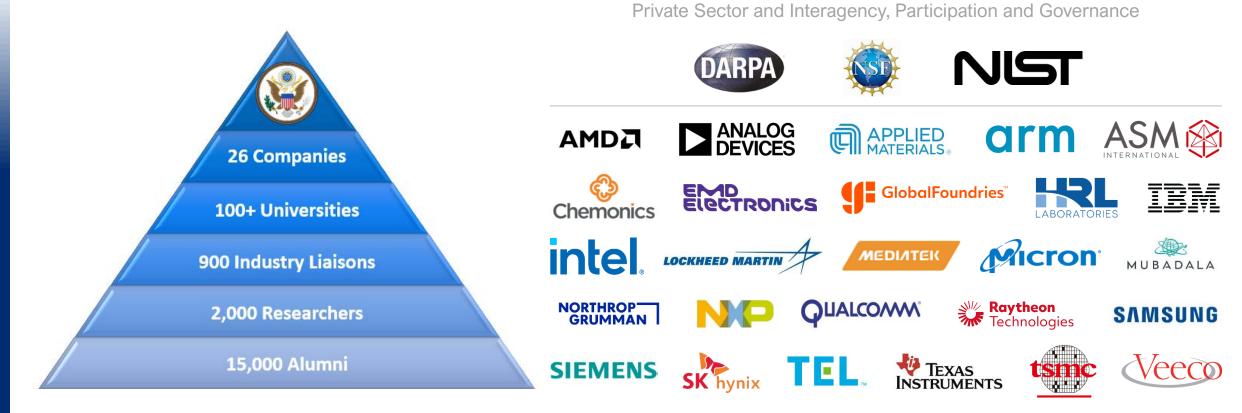

## **Premier Microelectronics Consortium Since 1982**

SRC is a neutral, trusted advisor that serves a vast network of engineers. All are dedicated to research, prototyping, and workforce training programs in advanced semiconductor technologies

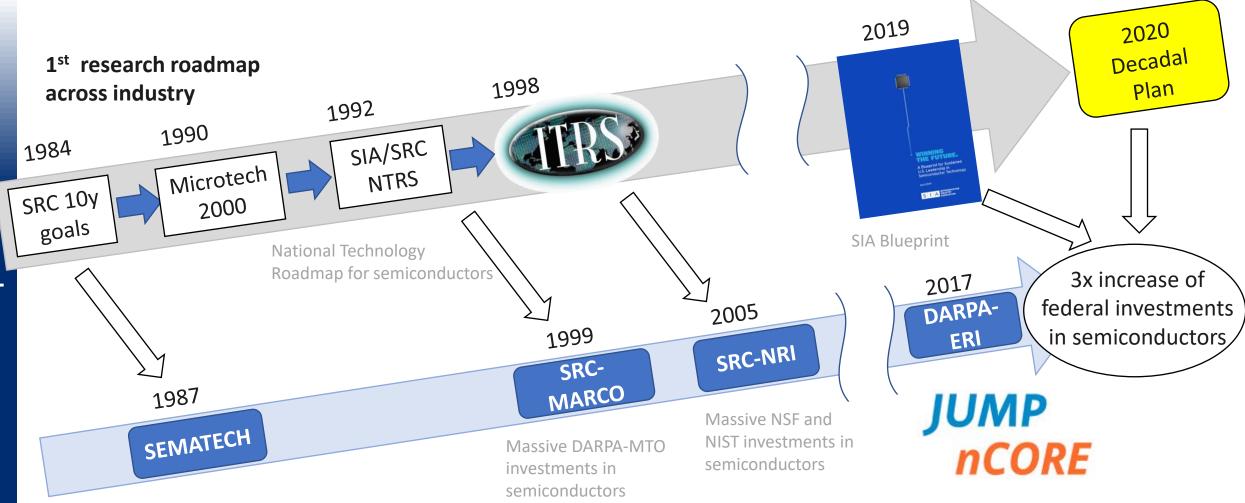

## **Thought Leadership That Positions Our Industry**

Semiconductor Research Corporation

## The "3 Ps" - SRC's Guiding Principles This Decade

### Prosperity

#### <u>Jan 2021</u>

Published Full 2030 Decadal Plan for Semiconductors

### 5 Seismic Shifts, ICT Drivers Call w/ SIA for $\uparrow$ Annual Funding

### The People

#### <u>Apr 2021</u>

Released SRC's Broadening Participation Pledge

Student Pipeline (AA,BS,MS,PhD) Greater Diversity, Equity, & Inclusion Ignite passion in US Citizens

### **The Planet**

| Data center<br>turn up | s                                  |

|------------------------|------------------------------------|

| the Earth's h          | Green processes<br>for green chips |

Images from <u>Samsung</u>

#### Oct 2021

Released SRC's Commitment to Sustainability

Green Materials & Processes Energy Efficient ICT Systems

7

#### Nov' 20 - Announced \$3.4 Billion Plan Aims to Stimulate US Semiconductor R&D

https://www.allaboutcircuits.com/news/newlyannounced-3point4-billion-plan-aims-stimulateus-semiconductor-rd/

https://www.src.org/about/decadal-plan/

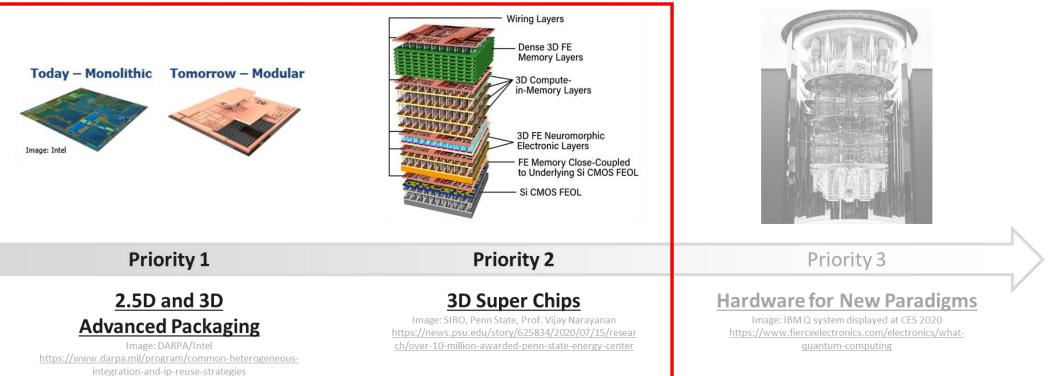

| Five "Seismic Shift" Research Priorities |                                             |  |

|------------------------------------------|---------------------------------------------|--|

| Smart<br>Sensing                         | The Analog Data Deluge                      |  |

| Memory<br>& Storage                      | The Growth of Memory and Storage Demands    |  |

| Communication                            | Communication Capacity vs. Data Generation  |  |

| Security                                 | ICT Security Challenges                     |  |

| Energy<br>Efficiency                     | Compute Energy vs. Global Energy Production |  |

# Heterogeneous Integration Roadmap Technical Working Groups

### **HI Market Applications**

- High Performance Computing & Data Center

- Mobile

- Medical, Health & Wearables

- Automotive

- IoT

- Aerospace & Defense

### **Heterogeneous Integration Components**

- Single Chip and Multi Chip Integration (including Substrates)

- Integrated Photonics

- Integrated Power Electronics

- MEMS & Sensor integration

- 5G & Beyond RF and Analog Mixed Signal

### **Cross Cutting topics**

- Materials & Emerging Research Materials Emerging Research Devices

- Supply Chain Security Thermal Management Reliability

### Integration Processes

- 3D +2D & Interconnect

- WLP (fan in and fan out)

### Design

SiP

- Co-Design

- Modeling & Simulation

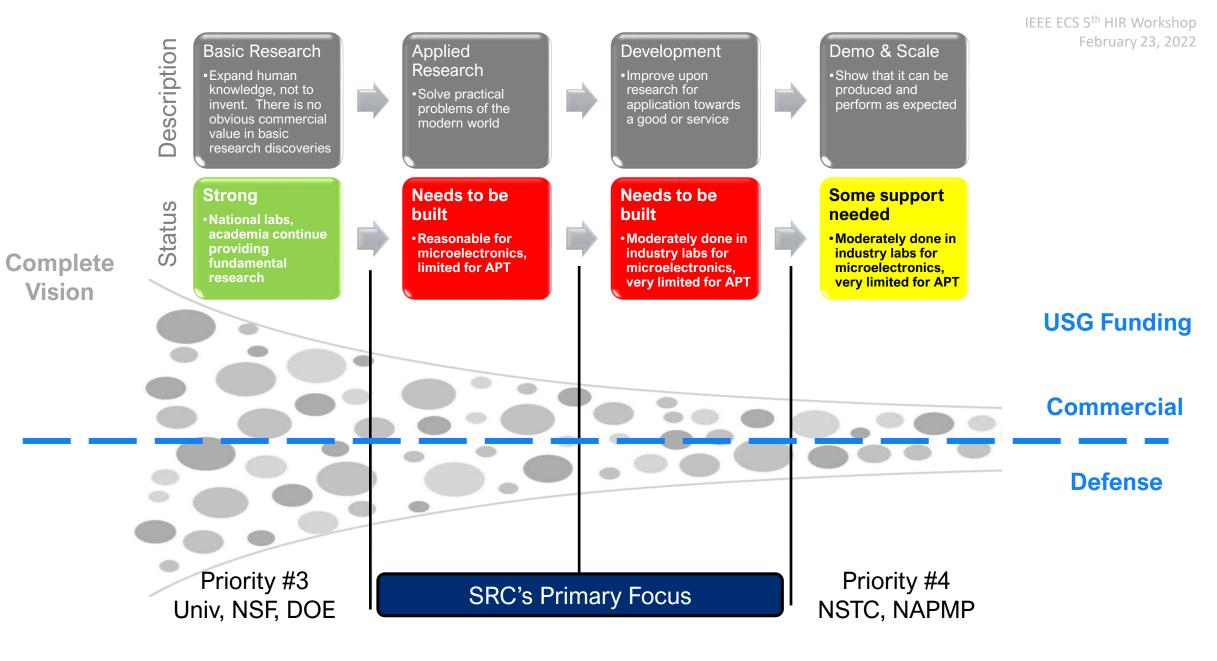

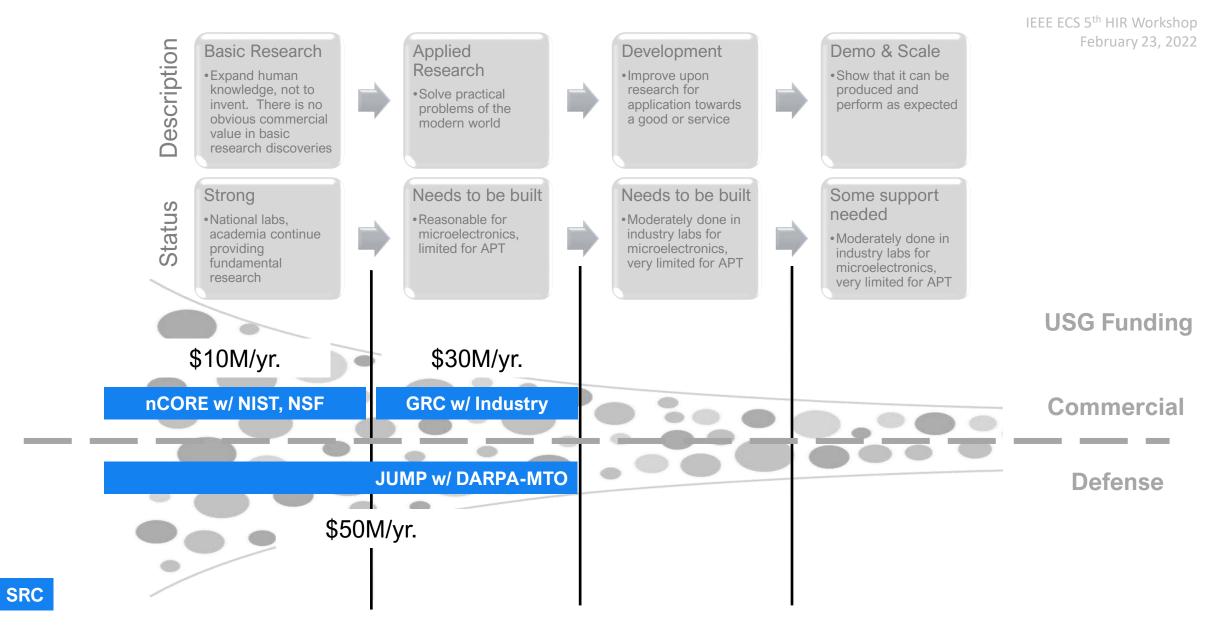

### Microelectronics & Advanced Packaging Technologies (MAPT)

We must evaluate market-driven opportunities "side-by-side" to realize lasting innovations

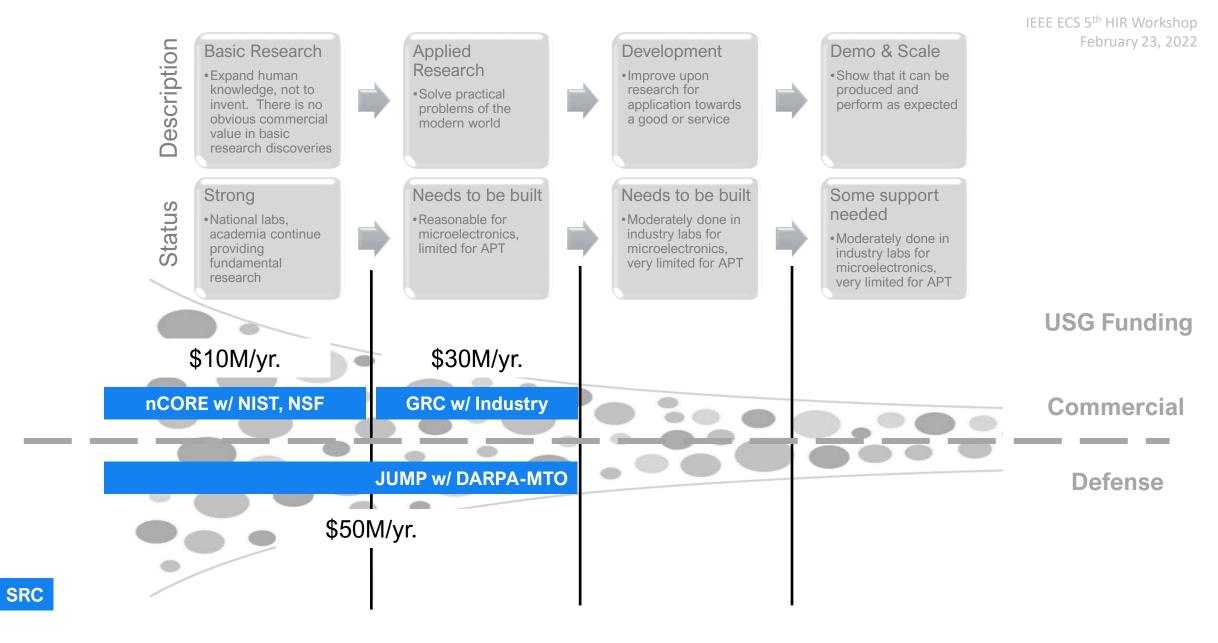

We need a Lab-to-Fab approach to MAPT Innovation. A robust pipeline from start to finish. SRC's 2030 Decadal Plan for Semiconductors is the "What" and the HIR is some of the "How." אר

Today

#### **GRC w/ Industry**

### **PKG**

### **CHIRP Center\***

### **ASCENT**

### **ComSenTer**

**UT/Arlington**

**33 Research Projects 15 Universities 53 SRC Scholars 37 Faculty Researchers** 73 Liaison Personnel

Ganesh Subbarayan Bahgat Sammakia

**13 Research Projects** 2 Universities **29 SRC Scholars 15 Faculty Researchers** 32 Liaison Personnel

Dir. Suman Datta

(Notre Dame)

AD Saveef Salahuddin (UCB)

## Dir. Mark Rodwell

(UCSB)

**JUMP w/ DARPA**

AD Ali Niknejad (UCB)

63 Research Projects **16 Universities 133 SRC Scholars** 42 Faculty Researchers 209 Liaison Personnel

**39 Research Projects 10 Universities 80 SRC Scholars 25 Faculty Researchers** 73 Liaison Personnel

\*CHIRP Center statistics are included in the overall GRC/PKG numbers

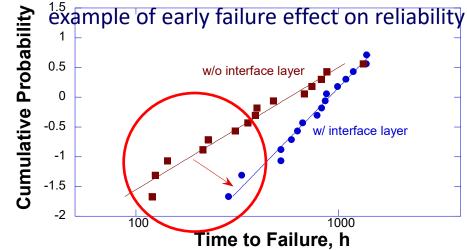

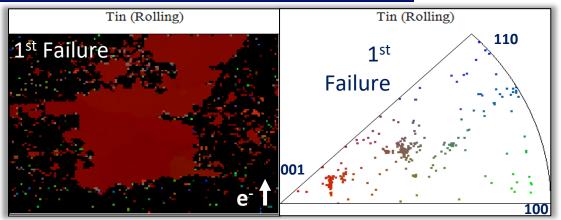

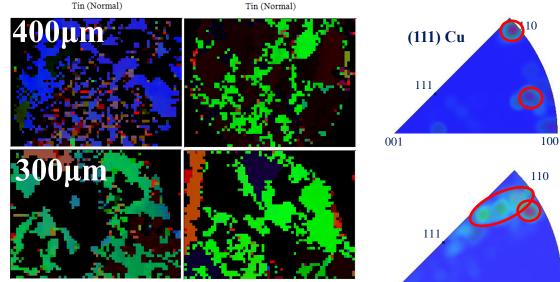

### Source of Early Failures and How to Suppress

#### Prof. Choong-Un Kim, UT/Arlington

#### Suppression of early failures

- may be most effective and practical in improving EM reliability

- our research finds that the early failures area always related to [001] Sn grain alignment to EM.

- [001] Sn effect can be suppressed by

- using Cu substate with controlled orientation (our study w/ Cu single crystal proven that Sn grain orientation is biased by Cu orientation)

- fine grain structure (but may not be practical)

EBSD characterization of EM failed samples reveals that early failed joint is with [001] Sn grain alignment.

Solder ball reflowed on single crystal Cu reveals that Sn grain <sup>10</sup> formation is biased. The bias effect is more in sma<u>ller solder.</u>

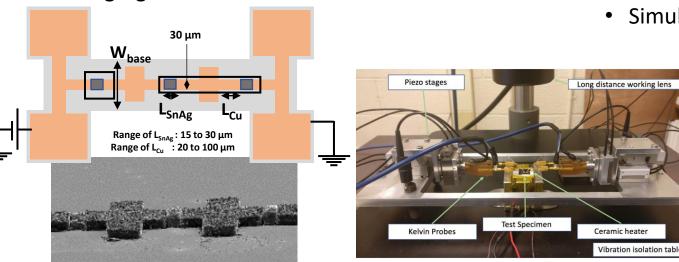

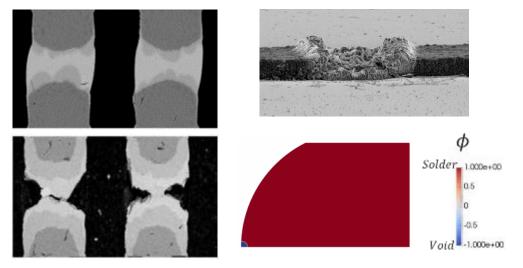

# Characterization of Sub-30 $\mu$ m Pitch $\mu$ -Bumps for Next Generation 2.5D Packages Ganesh Subbarayan and Carol Handwerker, Purdue University

#### Goals

- Electromigration characterization of sub-30  $\mu m$  pitch solder  $\mu\mbox{-bumps}$

- Characterization of electromigration influenced intermetallic growth and phase segregation

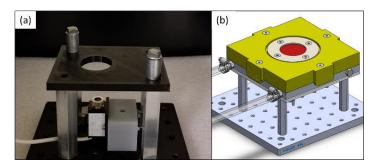

Nano-Resolution Probe Experimental Setup

#### Significant Results

- Designed and fabricated test device for testing sub- 30  $\mu m$  solder joints

- Developed electromigration test setup for use *in-situ* or *ex-situ*

- Simulated solder voiding using phase field models

High Thermal Interface Conductance Metrology

Amy Marconnet & Justin Weibel, Purdue University

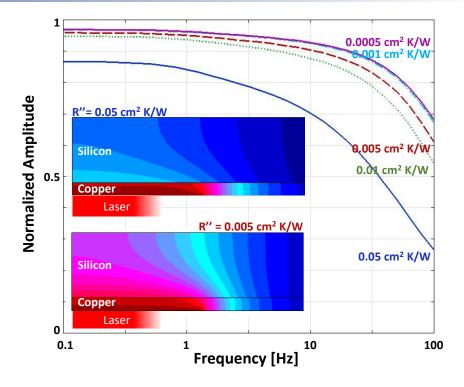

**Task Objective:** Develop, validate, and demonstrate a standardized, versatile, robust method for characterizing low thermal contact resistance interfaces ( $<0.01^{\circ}C\cdot cm^2/W$ ) applicable to a variety of different packaging applications

#### **Approach and Goals:**

- (1) Develop and optimize the experimental test fixture based on target applications

- (2) Construct the test fixture and validate the measurement based on benchmark interfaces that can be quantified with standard methods

Prototype test fixture for the radial Angstrom method using single layers samples that forms a starting point for developing the metrology technique for this task.

- (3) Demonstrate the low interface resistance measurement capability on applicationrelevant samples identified by the liaisons.

- (4) Develop analytical or hybrid (analytical + finite element) models to determine the thermal resistances for a multilayer stack as a function of the temperature evolution and (separately determined) material properties without measurement of absolute temperatures.

Preliminary COMSOL results for the temperature oscillation amplitude (at the top of the silicon layer) as a function of frequency and contact resistance for a Si-Cu interface. Insets show the amplitude as a function of position within the multilayer structure for two selected interfacial resistances.

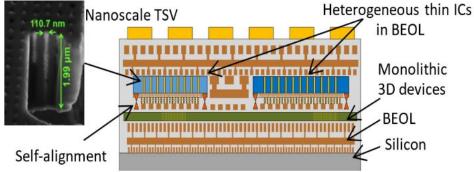

## Monolithic, Polylithic and Heterogenous 3D Integration

| Category                               | Granularity          | Technology                                                                                                                                                                                                    | Interconnect<br>Density (mm <sup>-2</sup> ) | Examples                                                                  |

|----------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------|

| 3D Transistor<br>(before M1)           | Transistor           | <ul> <li>Epitaxial growth         <ul> <li>Stacked nanosheet</li> </ul> </li> <li>Sequential Integration         <ul> <li>in situ dep and anneal</li> <li>layer transfer &amp; bonding</li> </ul> </li> </ul> | 10 <sup>9</sup>                             | C-FET Stacked Nanosheet MOS on FinFET NMOS                                |

| Monolithic 3D<br>(after M1)            | Gate, Block          | <ul> <li>Sequential Integration         <ul> <li>in situ dep and anneal</li> <li>layer transfer &amp;<br/>bonding</li> </ul> </li> </ul>                                                                      | >108                                        | Transpose SRAM 3D RRAM 3D RRAM 3D eDRAM 3D FEFET TCAN                     |

| Polylithic 3D<br>(W2W bonding)         | sBlock,<br>Chiplet   | <ul> <li>Parallel Integration</li> <li>Hybrid bonding</li> <li>Metal ALD</li> </ul>                                                                                                                           | 10 <sup>6</sup> – 10 <sup>8</sup>           | III W Switch Filter       LNA         SiO2-reconstituted tier in the BEOL |

| Heterogeneous<br>2.5/3D<br>Integration | Chiplets,<br>modules | <ul> <li>3D Packaging</li> </ul>                                                                                                                                                                              | 10 <sup>4</sup> – 10 <sup>5</sup>           | Stacked and assembled chiplets<br>on glass interposer                     |

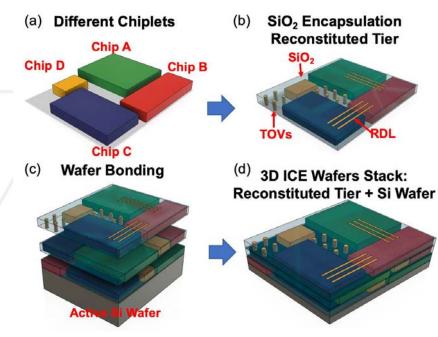

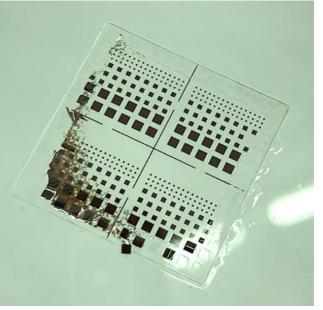

## **Examples of Heterogeneous Integration Technologies from Georgia Tech's Integrated 3D Systems Lab (i3DS)**

Pseudo-monolithic 3D: *heterogeneous* integration of device tier *within/near the BEOL*

SiO<sub>2</sub>-reconstituted-tier mounted on a glass wafer

'Sea of Chiplets"

Smallest chiplet: 10x10 μm

M.-J. Lai and M. Bakir, IEEE TCPMT 2021 (Early Access)

Georgia

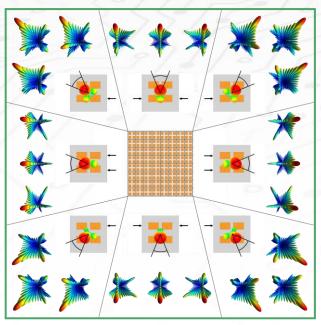

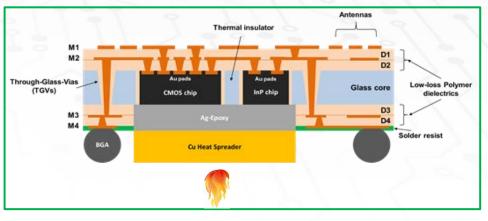

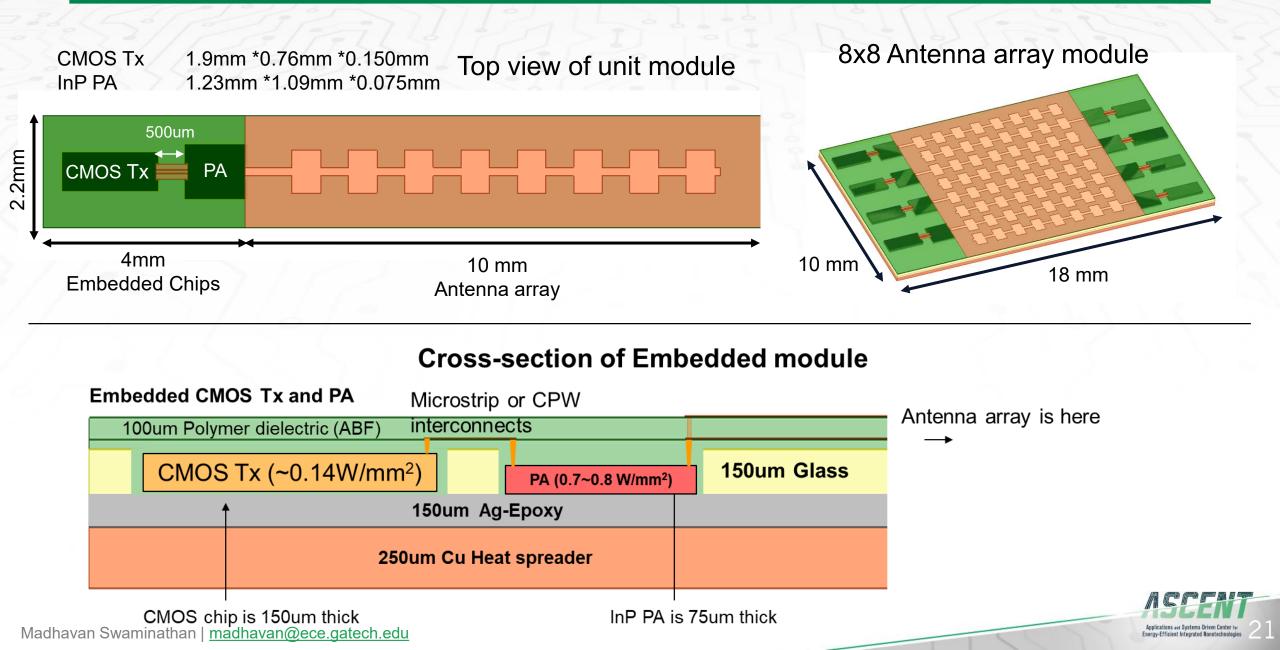

# **Addressing the Three Challenges: Technical Approach**

16x16 = 256 patches

64 sub-arrays, each driven by a PA

#### Antenna in Package

### □ Antenna in Package

- Hybrid Beamforming Architecture

- Large 2D Array for Full Field of View (Tx)

- 2x2 Sub-Array

- 2D Butler Matrix

- 1D Array for Rx

# Switch PA A A

2x2 sub-array

with Butler Matrix

Minimizing Package Loss

- Minimizing Package Loss

- Embedded IC

Beamformer

- Eliminate assembly

- High frequency polymer layers

- Low loss interconnects

- Electronics beneath antenna

### Heat Removal

#### Heat Removal

- Thru cavities in Glass

- Exposed IC

- Thermal Interface Material

- Heat Spreader

- Minimize thermal resistance

Madhavan Swaminathan | <u>madhavan@ece.gatech.edu</u>

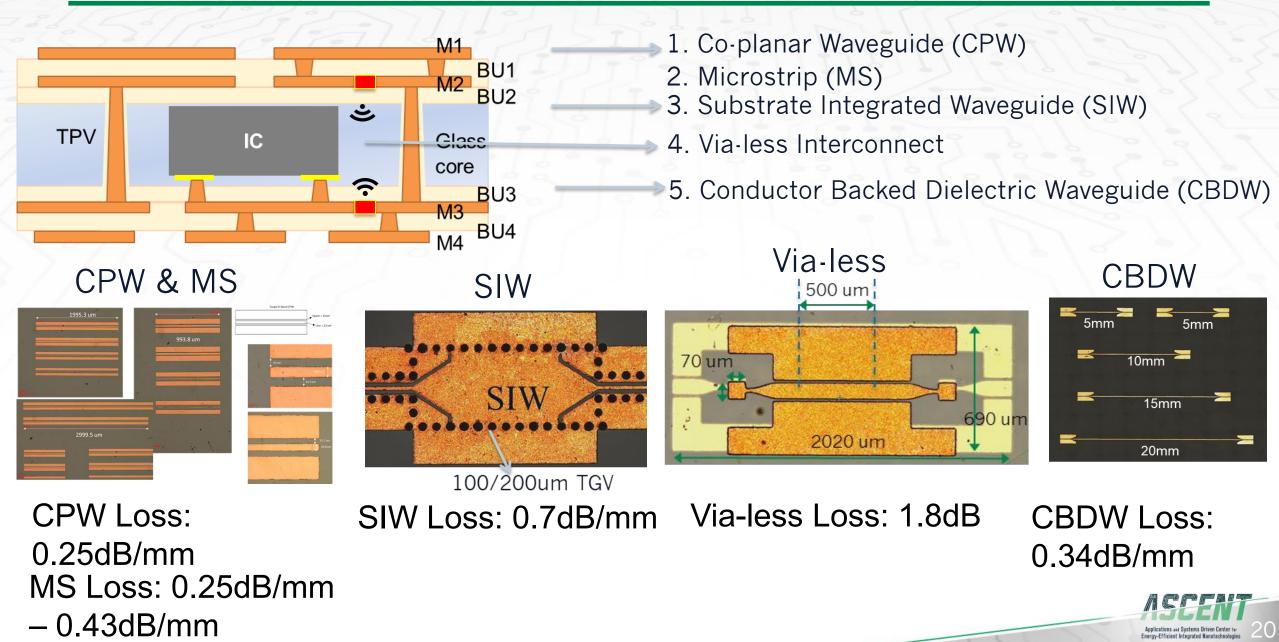

# **D-Band Interconnects**

## 140GHz 8x8 Array Functional Module (w/ ComSenTer)

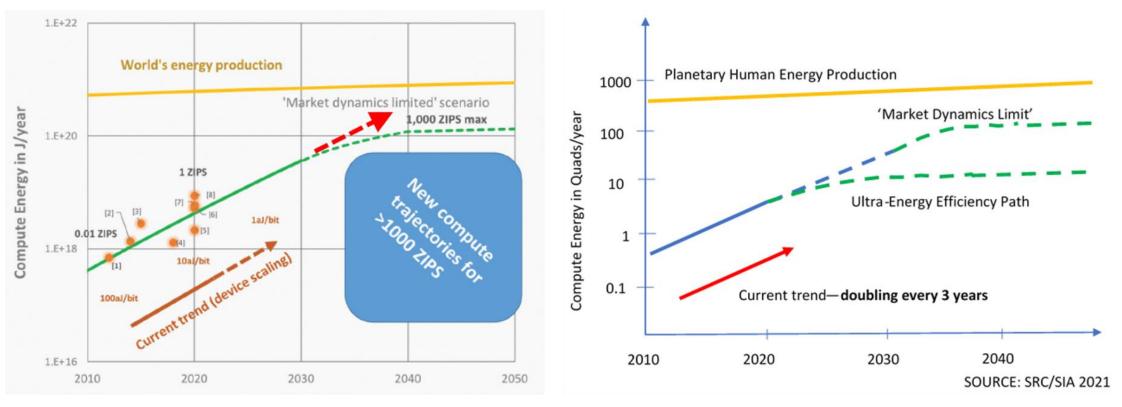

Seismic Shift 5. Compute Energy vs. Global Energy Production, Task ID: 2778.044

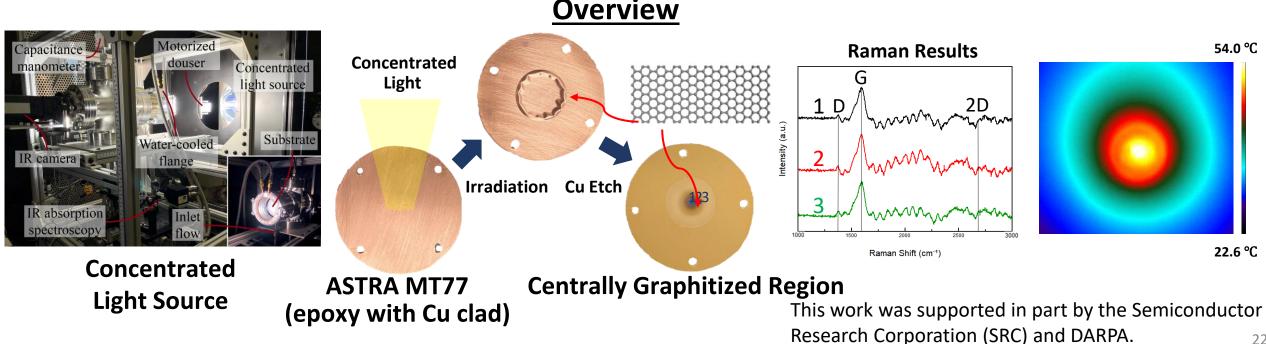

### Thermally Enhanced Organic Substrates for GaN Power Amplifiers

Student: Min Jong Kil, Sam Ellison Faculty: Timothy S. Fisher – Mechanical and Aerospace Engineering, UCLA

### **Task Focus and Goal**

- Improve heat removal capability of organic substrates in high-power GaN power amplifiers

- Enhance thermal management with a ten-fold reduction in heat spreading resistance

### **Technical Approach**

- Green manufacturing: 10 kW<sub>e</sub> concentrated simulated solar source with a maximum controllable peak flux of  $4.5 \text{ MW/m}^2$

- Epoxy is converted into graphitized layers by short-duration, high-flux irradiation in vacuum

JRC

Today

IEEE ECS 5<sup>th</sup> HIR Workshop February 23, 2022

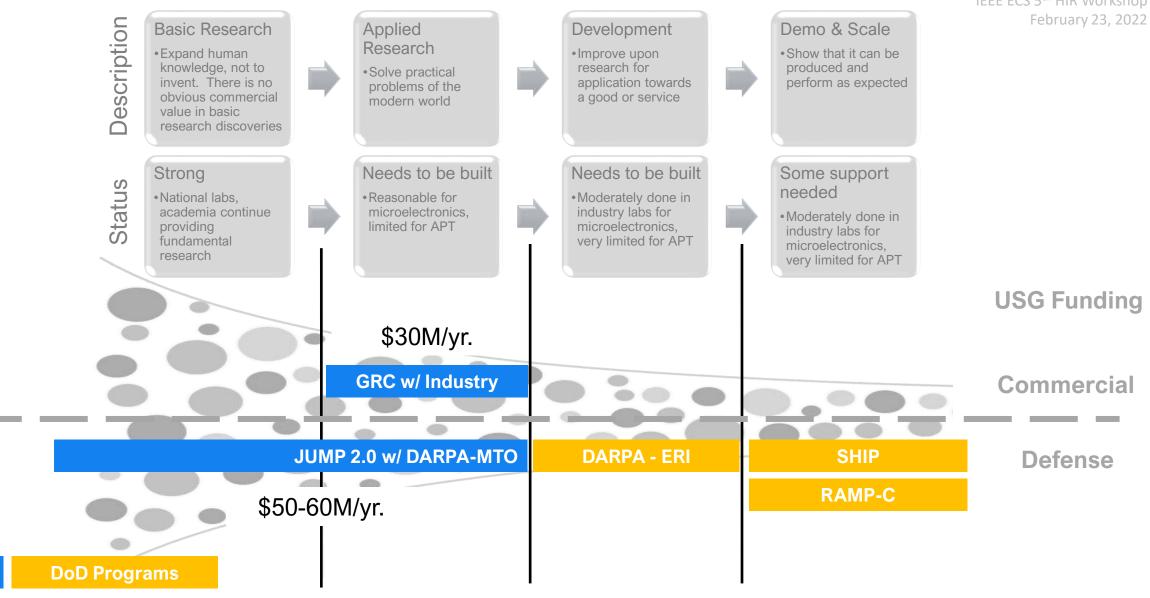

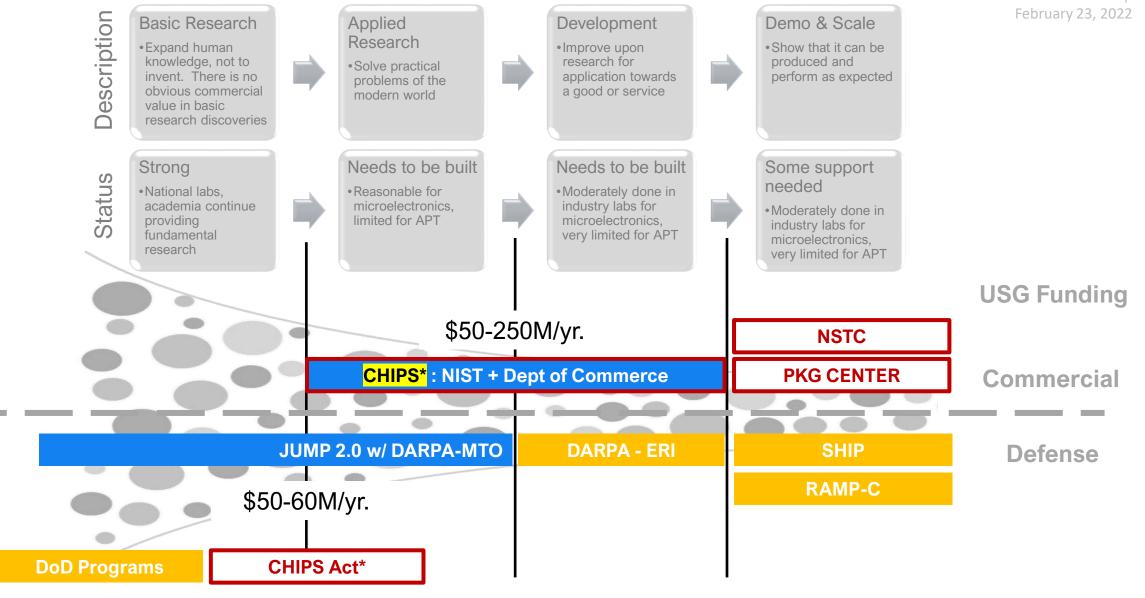

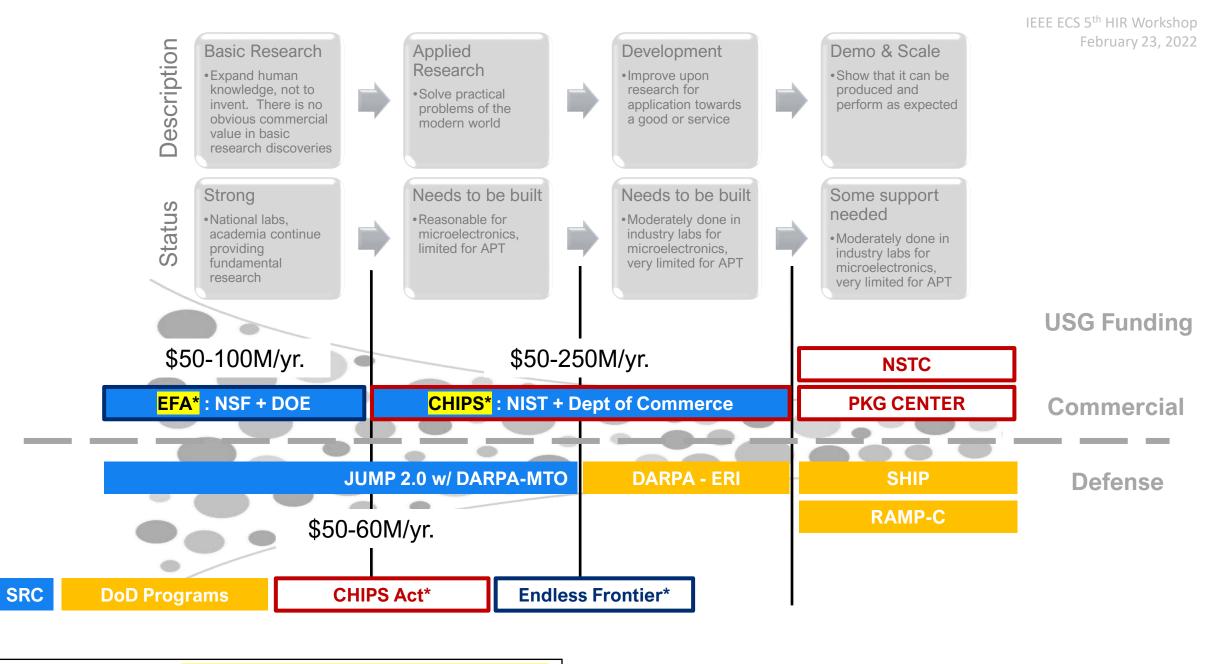

Jan 2023+. Announced JUMP 2.0 with DARPA. Center & individual whitepapers due March 7<sup>th</sup>, 2022.

SRC

JSC

24

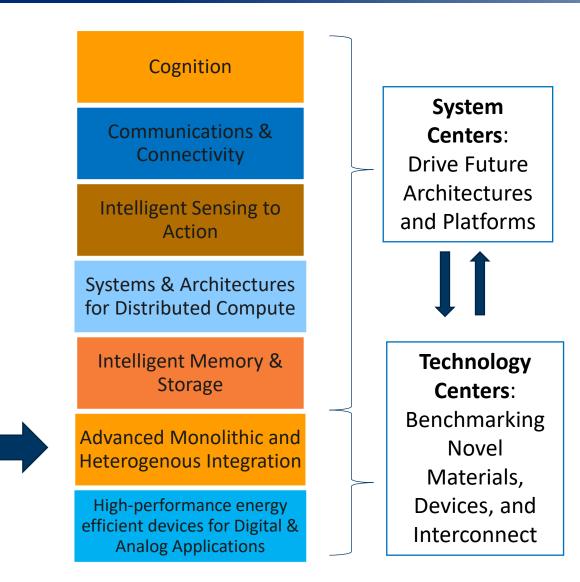

# JUMP 2.0 Focus Centers

- System Centers: what are the technology implications?

- Technology Centers: what are the architectural implications?

- Target budget per Center: \$5M-\$7M/yr.

- Right-size for Critical-mass & Critical Mind Share.

- Recommended:

- ~20 Pls\*

- Median task size: ~\$250k/yr.

- # of Universities not specified; find a balance.

(See <u>FAQs</u>, Q4)

IEEE ECS 5<sup>th</sup> HIR Workshop

With anticipated CHIPS ACT funding; \*Congressional legislation pending

SRC

JSC

## Why SRC is the Right Organization to Lead

- Low risk. A 40-year history of working with companies, universities, and governments across many innovation programs

- Often sited as the go-to organization for Industry- Government- Academic collaboration

- A Non-profit, neutral 3<sup>rd</sup> party with nothing to gain and no ulterior motives or outside influences

- Bringing industry for effective technology transfer that benefits the university and the market

- Develop technology that's shaped the industry for 40 years

- Consistently builds communities where they are needed

- Membership contracts active with 26 industry members and 3 gov't agencies, research contracts active with 100+ universities

- Existing processes for defining meaningful research agenda that generates results and partnering with government

- In-house Technical Program Managers including Industrial Researchers, Contracting, Program Management, Billing, User portal, Legal, etc.

In 2021,

\$90M

JRC

# J $\mathbf{n}$ đ Futu

We need an aspirational new narrative that ignites the next generation of talent

Drive holistic, optimal solutions in HW/SW through interlocked multidisciplinary research

Help students see we have hard yet interesting problems that can't be solved without them

Convey to students that opportunities are abound for the next 20-30 years

Create industrial relationships and internship experiences that provide insight into SOTA\*

IEEE ECS 5<sup>th</sup> HIR Workshop

February 23, 2022

## **Compute Energy vs. Global Energy Production**

Seismic Shift #5

2030 Decadal Plan for Semiconductors

DOE-AMO Workshop, Apr 21-23, 2021

This is not only critical for our society and planet, but sustainable microelectronics can win the hearts & minds of young innovators.

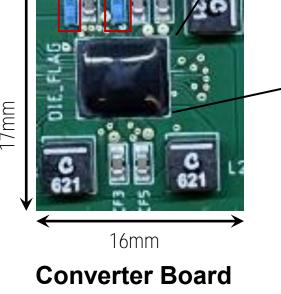

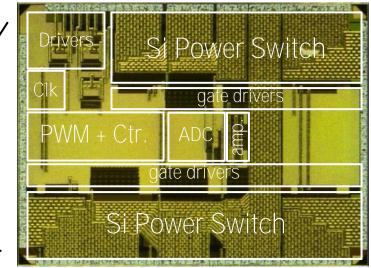

## High Voltage DC-DC Converter with Packageand Board-level GaN/Si Integration

- Optimized design with high-performance low-voltage Si devices with high-voltage GaN devices

- Breakthrough efficiencies for 48V-to-1V and 24V-to-1V conversions.

- Compact design for high energy-density

| Topology               | 3-level hybrid Dickson       |        |

|------------------------|------------------------------|--------|

| Area                   | 16mm x 17mm                  |        |

| Input Voltage          | 48V                          |        |

| Output Voltage         | 0.7-1V                       |        |

| GaN FETs               | Enhanced mode GaN            |        |

| Inductor               | 3 x 0.62uH                   | ,<br>, |

| Peak Efficiency        | 90.4%@48-1V, 1MHz            |        |

| <b>Current Density</b> | 240/ *955A/inch <sup>3</sup> |        |

**GaN FETs**

#### Die shot and characters

| Technology      | 180nm HV BCD                       |

|-----------------|------------------------------------|

| Area            | 4mm x 3mm                          |

| Si Switch       | 24V/20V/16V/12V/6V<br>N-type LDMOS |

| V <sub>DD</sub> | 5V                                 |

\*Component area only Latest Prototype

## **Call to Action**

- The ICT opportunities of tomorrow are simply **unachievable with emerging hardware technologies** as the underlying hardware is up against fundamental physical limits.

- A crisis is at hand, where the hardware paradigm must shift to create the desired value with **3D microelectronic** and **advanced packaging technologies (MAPT) as the key driver**.

- To stay at the leading edge of hardware innovation, we must invest in early-stage ideas and tech maturation, exploring options through a **fast-fail** and **tech-transfer mindset**.

- It is equally important that we are committed to workforce development and broadening participation.

- We must seek and create energy efficient systems via eco-considerate manufacturing.

- There is a bright future for semiconductors, but we must change our own narratives to win over the hearts and minds of next gen innovators.

Investment in Heterogeneous Integration is priority #1. We must act, now!

JSC

## **SRC's Mission For The Roaring 20s**

Semiconductor Technology Leadership

2030 Decadal Plan for Semiconductors

**Diverse Student Pipeline**

Broadening Participation Pledge

Eco-Considerate Processes and Systems

<u>Commitment to Sustainability</u>