# Research Fab Germany (FMD): Bridging Chip Design to Applications Through Heterogeneous Integration

- Spokesman of the Fraunhofer Group for Microelectronics and Chairman of the steering committee of the Research Fab Microelectronics Germany

- Executive Director of the Fraunhofer Institute for Integrated Circuits IIS

- Head of the Chair of Information Technologies at the

- Friedrich-Alexander-Universität Erlangen-Nürnberg

23.02.2022

A cooperation of

🖉 Fraunhofer

An overview

FMD combines the expertise and infrastructure of **13 research institutes** across Germany and offers developments **along the entire value chain in a one-stop shop.**

FMD at a glance:

3,000 m EUR in assets 3,500 employees FTE, 2,000+ scientists 600 m EUR/yr 250 m EUR/yr from Industry From TRL2 to TRL8 **Total investment of EUR 350 million** for additional infrastructure and future developments. (1.4.2017-30.9.2021)

SPONSORED BY THE

Federal Ministry of Education and Research

International establishment of FMD and cooperation with European partners (e.g. NGC Alliance).

A cooperation of

2

23.02.2022 FMD

Technology Platforms of FMD

#### Optoelectronic Systems

Power Electronics

MEMS Actuators

Microwave and Terahertz

Sensor Systems

Two other technology platforms are currently under construction: Advanced System Integration and Advanced System Design

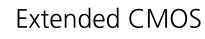

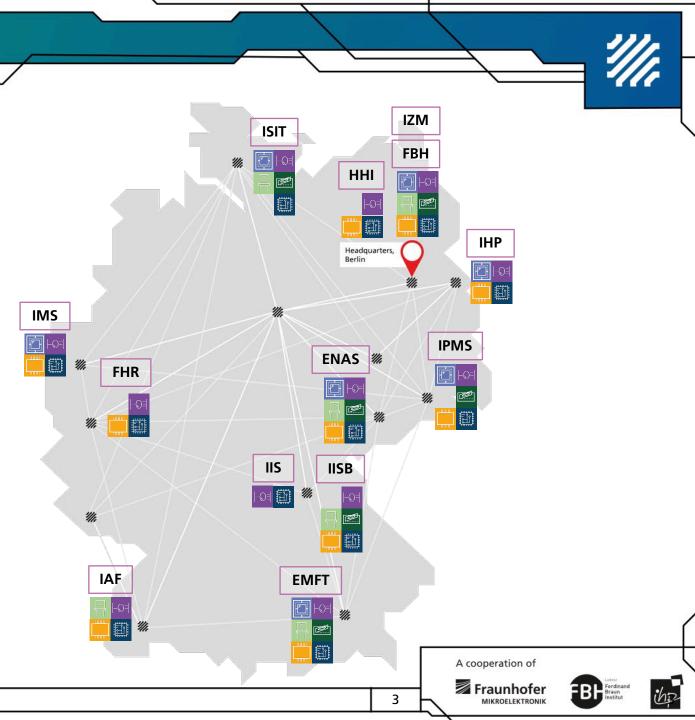

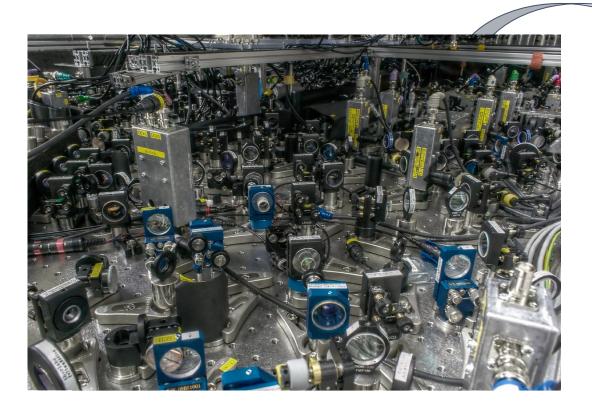

FMD Cleanrooms all over Germany

- Operation concepts in alignment

- Over 2.200 equipment in 13 cleanrooms all over Germany

- Over 10 Mio moves per year

A cooperation of

- Overall size: appr. 11.000 m<sup>2</sup>

- Wafersizes:

2" till 300 mm

Organization

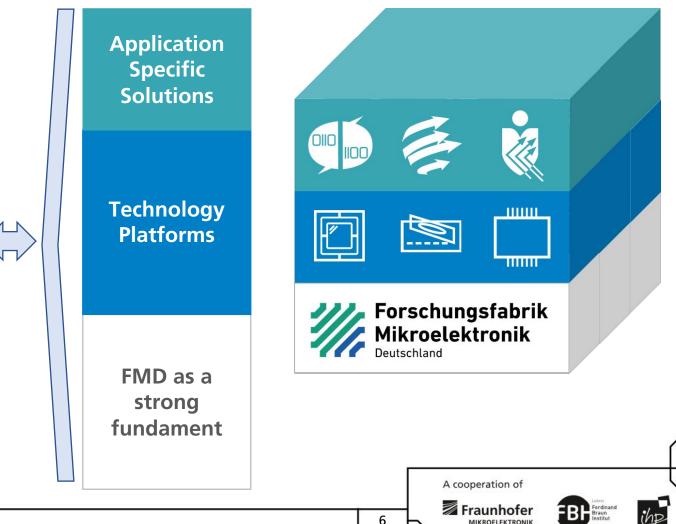

Application Specific Solutions

Technology Platforms

FMD as a strong fundament

FMD

23.02.2022

6 specific application topics with collaborative advantage

6 technology platforms along the value chain

13 member institutes of the Fraunhofer-Gesellschaft and Leibniz-Gemeinschaft all over Germany

- Transport and Smart Mobility

- Digital Industry

- Health and Wellbeing

- Energy

- Digital Life

- Civil Security and Occupational Safety

5

A cooperation of **Fraunhofer**

MIKROELEKTRONIK

- Extended CMOS

- Optoelectronic Systems

- Power Electronics

- MEMS Actuators

- Microwave and Terahertz

- Sensor Systems

Heterogeneous Integration Roadmap and FMD (Research Fab Germany) Many synergies between HIR and FMD

IEEE-HIR (Heterogeneous Integration 1// Roadmap)

**CHAPTER 2: HIGH PERFORMANCE COMPUTING AND DATA CENTERS** CHAPTER 3: INTERNET OF THINGS (IOT) **CHAPTER 4: MEDICAL, HEALTH & WEARABLES CHAPTER 5: AUTOMOTIVE CHAPTER 6: AEROSPACE AND DEFENSE CHAPTER 7: MOBILE CHAPTER 8: SINGLE CHIP AND MULTI CHIP INTEGRATION CHAPTER 9: INTEGRATED PHOTONICS CHAPTER 10: INTEGRATED POWER ELECTRONICS CHAPTER 11: MEMS AND SENSOR INTEGRATION CHAPTER 12: 5G COMMUNICATIONS CHAPTER 13: CO-DESIGN FOR HETEROGENEOUS INTEGRATION CHAPTER 14: MODELING AND SIMULATION CHAPTER 15: MATERIALS AND EMERGING RESEARCH MATERIALS CHAPTER 16: EMERGING RESEARCH DEVICES CHAPTER 17: TEST TECHNOLOGY CHAPTER 18: SUPPLY CHAIN CHAPTER 19: CYBER SECURITY CHAPTER 20: THERMAL CHAPTER 21: SIP AND MODULE SYSTEM INTEGRATION CHAPTER 22: INTERCONNECTS FOR 2D AND 3D ARCHITECTURES** CHAPTER 23: WAFER-LEVEL PACKAGING (WLP) **CHAPTER 24: RELIABLITY**

FMD: Technologies and Applications

MIKROELEKTRONIK

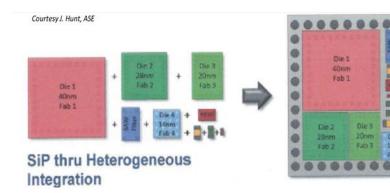

#### Heterogeneous Integration

Strategy

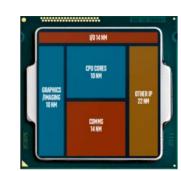

SoC System on Chip

Package Integration

# Drivers for Heterogeneous Integration in the HPC Segment

Die cost per unit area increasing with node shrinks

Package IO, latency/BW and power constraining

> It is all about transferring data!

# Heterogeneous Integration provides a solution that can be in many formats

Wafer-Level Hetero-Integration

Board-Level Hetero-Integration

% Specific/different applications

23.02.2022 FMD

7

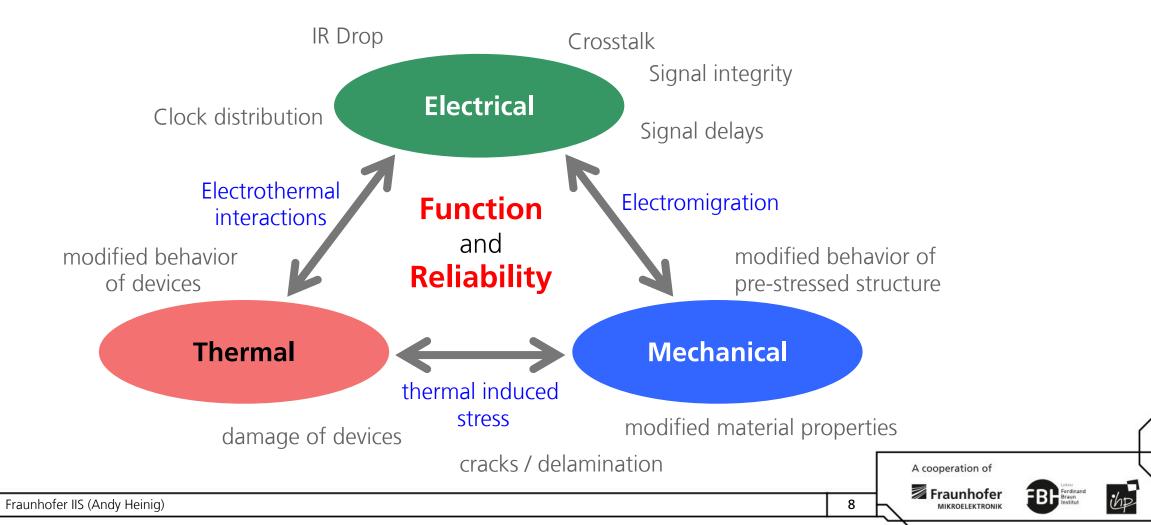

Ultra compact miniaturized systems bring new combined physical effects:

23.02.2022

Influences all design steps across all hierarchy levels

## System design

- % Chip-package or chip-package-board-co-optimization necessary

- **W** First tools available to solve parts of the whole problem

- System implementation and system verification

- Block implementation (analog, digital) can be done by existing flows and tools

- Mew methods necessary on the boarder between block implementation

- Power delivery networks much more complex

- Interface definition and standardization between different dies

Interconnects for 2D and 3D architectures

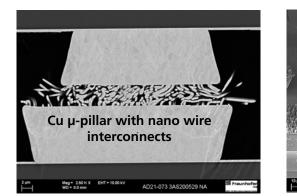

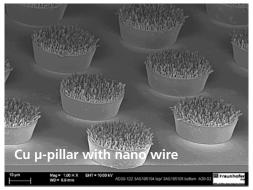

## % Cu-Nano Wire

- # High-density interconnects for D2W and W2W Bonding

- Room temperature bonding, fluxless process, single metal (Cu)

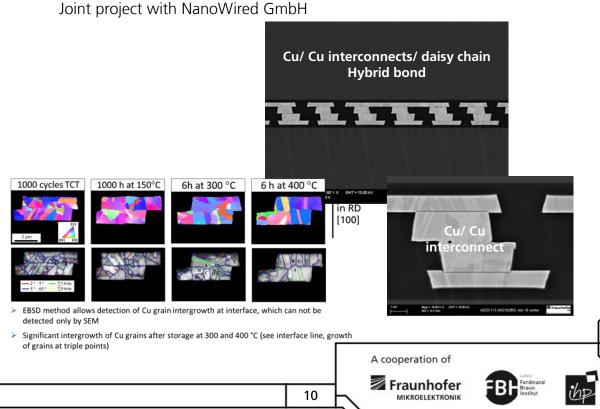

## % Cu/Cu Hybrid Bonding

- # Hybrid bonding on 300mm wafer size qualified

- W2W Bond alignment accuracy (~1µm)

- Bond process established

- # Low Temp. processes < 200°C</p>

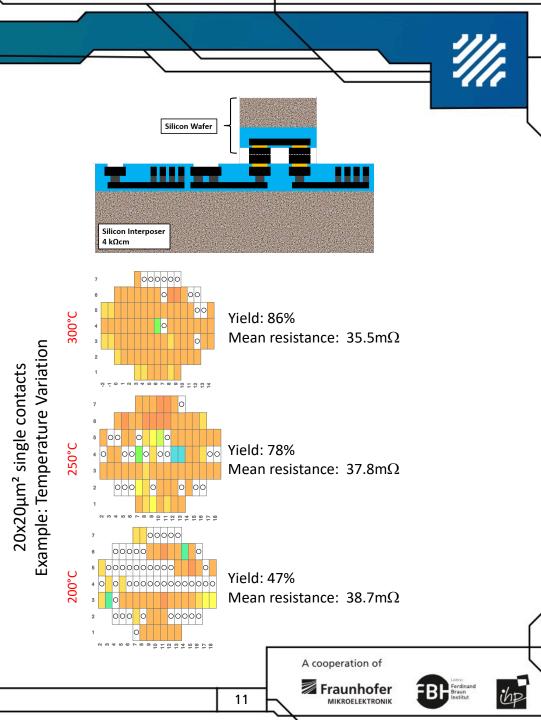

Wafer-level Heterogeneous Integration for advanced RF applications

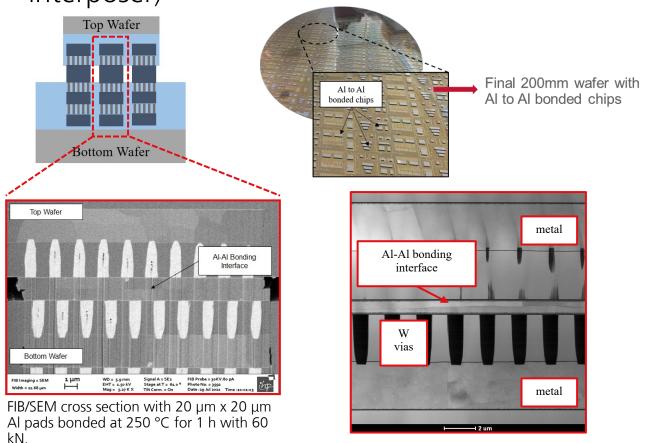

- High-Vacuum Al-Al bonding for 8" wafer platform *'//,*

- SiGe-BiCMOS co-integration platform (e.g. on Si-RF-11. interposer)

Leibniz IHP (Matthias Wietstruck)

23.02.2022

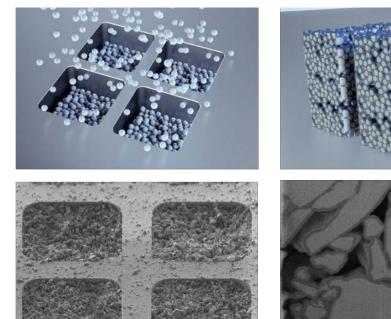

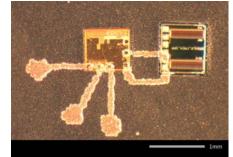

Powder MEMS: Unique BEOL-Compatible 3D Integration

**Powder MEMS: substrate-level integration of three-dimensional functional microstructures**

1. Dry-filling of micromolds

3. Substrate conditioning for post-processing

Unique set of characteristics: Wide selection of materials Substrate-level integration Low process temperature No organic binder BEOL compatible Lateral dim.: 30 – 4000 µm Withickness: 30 – 1000 µm

12

Novel wafer-level integrated microcomponents like 3D micromagnets, porous microfluidic structures etc.

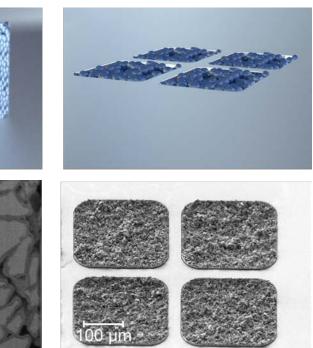

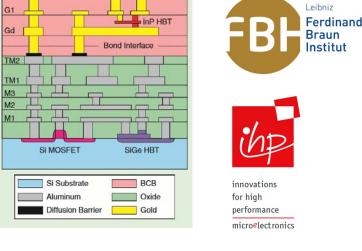

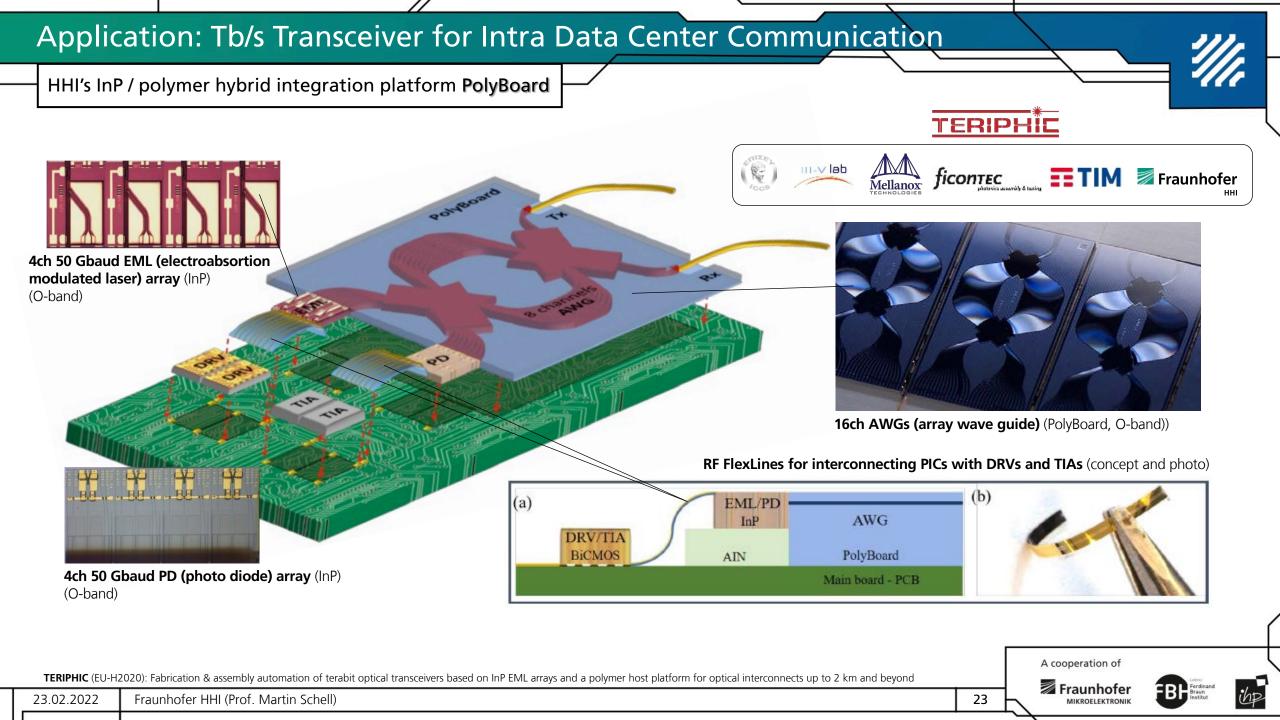

InP-on-BiCMOS

Combining benefits of III-V technology with BiCMOS

Integrating InP and BiCMOS circuits on a single chip FBH bipolar InP process

# IHP BiCMOS process

**Wafer-bonding and final processing steps in III-V line**

# High-frequency performance up to 300 GHz, for 6G and sensors

Key functions demonstrated

- Millimeter-wave frequency sources 160 ... 330 GHz

- W-band up-converter and transmitter

13

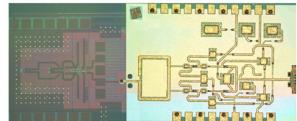

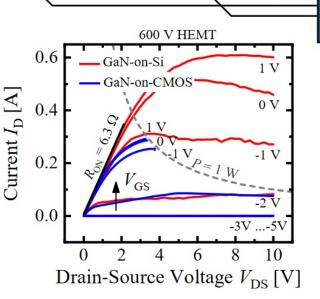

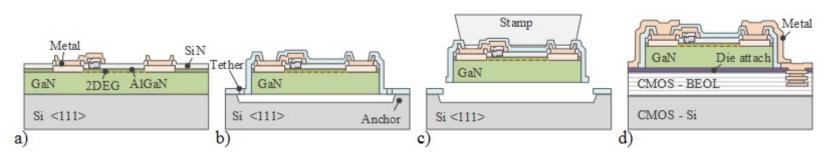

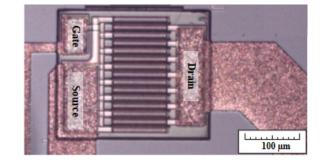

GaN-HEMTs on CMOS Technology by Micro-Transfer-Printing

- Monolithic integration of GaN and CMOS devices very challenging due to material and thermal mismatches

- GaN device source wafer, CMOS device target wafer

- Substrate removal of GaN devices and transfer

IV-data on Si and on CMOS

#### GaN-on-CMOS fabrication steps by transfer printing Hetero-integrated GaN-HEMT on CMOS

R. Reiner, R. Lerner, P. Waltereit, N. Hansen, S. Moench, A. Fecioru, and D. Gomez, "Characteristics of Hetero-Integrated GaN-HEMTs on CMOS Technology by Micro-Transfer-Printing," 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2021, pp. 323-326

23.02.2022 Fraunhofer IAF (Dr. Patrick Waltereit)

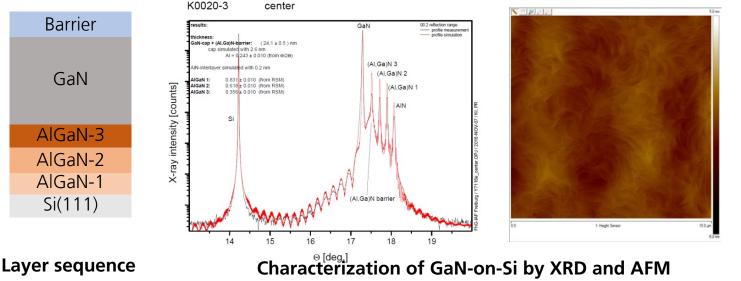

Epitaxial growth of GaN layers on Si(111) substrates

- GaN-based epitaxial films are grown on large area 200 mm Si 11. substrates by MOCVD

- Tuning of growth parameters to compensate lattice and thermal mismatches

- Alternative to expensive high-resistivity SiC substrates

- Integration of III/V material into CMOS fabrication

3x200 mm MOCVD reactor for GaN-on-Si devices

15

#### Layer sequence

23.02.2022

Fraunhofer IAF (Dr. Patrick Waltereit)

Fraunhofer MIKROFLEKTRONIK

A cooperation of

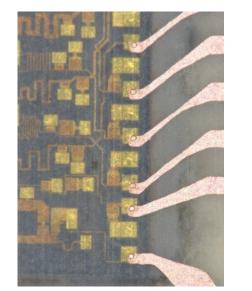

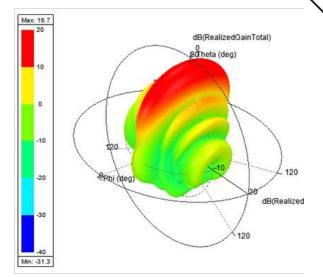

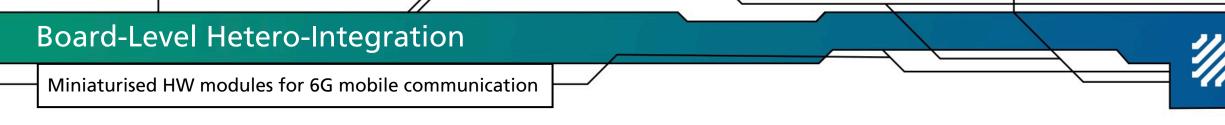

#### **Board-Level Hetero-Integration**

PCB Embedding for 5G/Millimeter-Wave Applications

- Integration of antennas with RF front-end enables efficient beamforming and multi-user access at millimeter-wave frequency band

- Approach: PCB embedding of GaN and SiGe ICs in antenna-in-package for scalable 5G front-end module

- RF characterization of embedding technology

- Electrical and thermal design of antenna-inpackage modules

- Short interconnect between IC and antenna

TECHNIK**UN**

Fraunhofer IZM (Dr. Ivan Ndip)

23.02.2022

EPIGAN

ERICSSON

- Development of an ultra-broadband and miniaturized massively MIMO D-band HW module with integrated beamforming capability for 6G

- Implementation of new baseband architectures taking into account parasitic THz effects in the D-Band module

- Development of new test procedures and environments for the validation of the modules

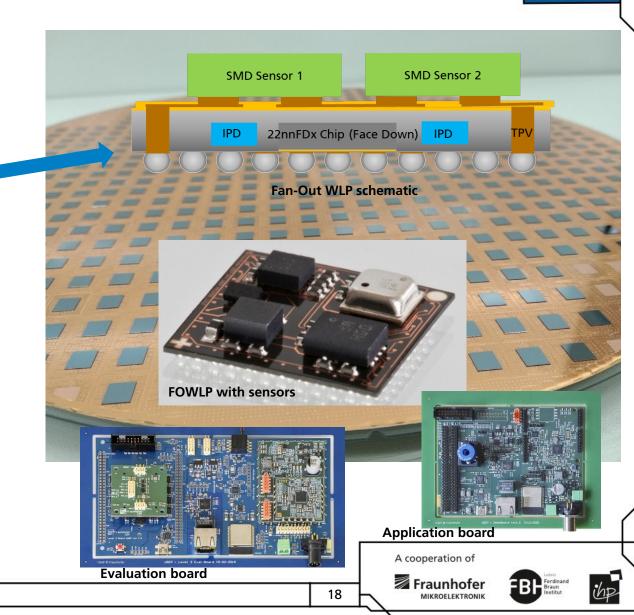

#### Application: Sensor platform for next generation electronics

Universal Sensor Platform (USEP)

- Development of universal sensor platform (USEP), with which even smaller system providers can shoulder the growing development and production effort for next generation electronics

- # Embedded chips

- Package-size: 10mm x 10mm x 0.2mm

- # 4 layer thinfilm redistribution

- SMD-assembly of different sensors on top

- Assembly of complete sensor system on evaluation and application boards

- System level validation and functionality demonstration

MEMS for underwater US

ECSEL

H2020 Project: SILENSE

Bundesministeriun für Bildung

und Forschung

# Integration of MEMS and ASICs for touchless control and gesture sensing with ink-jet printed conductive tracks

Application: (Ultra)-Sound Interfaces and Low Energy Integrated Sensors

- Mapted process flows under ongoing development for

- MEMS for airborne US with fragile (~300nm thick) membranes

→ Integrity of sensitive membranes demonstrated, stress-decoupling concept under development

→ Adapted process flow demonstrated, performance testing ongoing

(infineon NP SAL SILICON AUSTRIA LABS TU/e

19

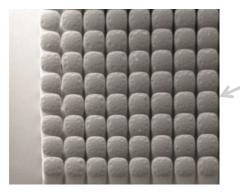

#### Application: Piezoelectric MEMS Energy Harvester

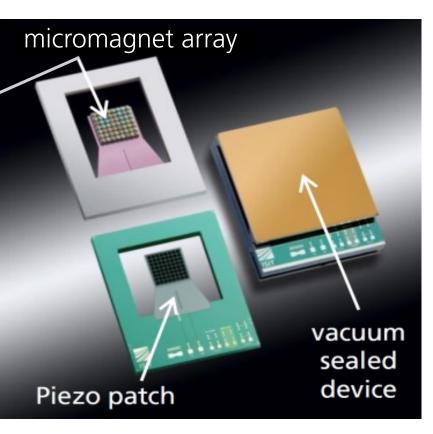

Wafer-level integrated 3D NdFeB micromagnets

NdFeB micromagnet array solidified with  $Al_2O_3$ .

Each pixel is 250 x 250  $\mu$ m<sup>2</sup> wide and 500  $\mu$ m high.

Br  $\approx 350$  mT, Hc  $\approx 1$  T/ $\mu_0$

## **Integrated 3D NdFeB** micromagnets allow for

**W** Contactless magnetic excitation

- Harvesting of rotary and translational movements

- Broadband frequency range (1 Hz – 2 kHz depending on excitation)

- Compact design and highpower density due to high tip density

20

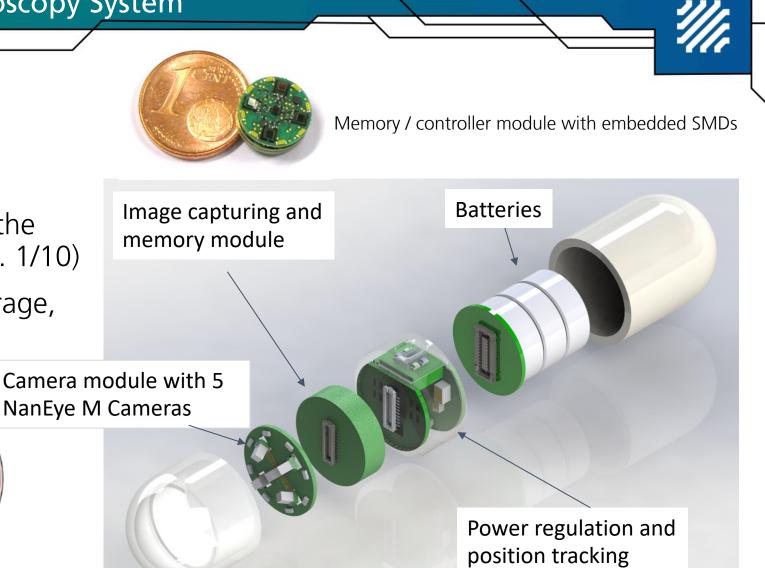

#### Application: Modular Capsule Endoscopy System

Project EndoTrace

- Use of different miniaturization techniques (e.g. Module stacking, embedding, semi-flex)

- Reduce number of images during the passage through the body (approx. 1/10)

- Onboard image capturing and storage, no external devices needed

small intestine

herapeutic Smart Pill

GEFÖRDERT VON

ür Bildung

und Forschung

000

ovesco

**Diagnostic Smart Pills**

endo*Trace*

21

A cooperation of

#### **Application: Sensor Systems For High Performance Sails**

Project SenSail

- Textile-integrated measuring system (force / pressure / position and orientation in space)

- Development of a bus system adapted to large textiles (~70m<sup>2</sup>)

- Integration of sensor nodes in a high-performance sail

- Development of a portable and wireless data evaluation unit

Bundesministerium ür Wirtschaft

und Energie

A cooperation of

TEC

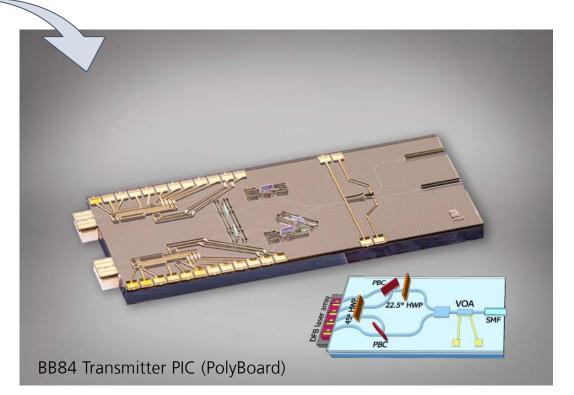

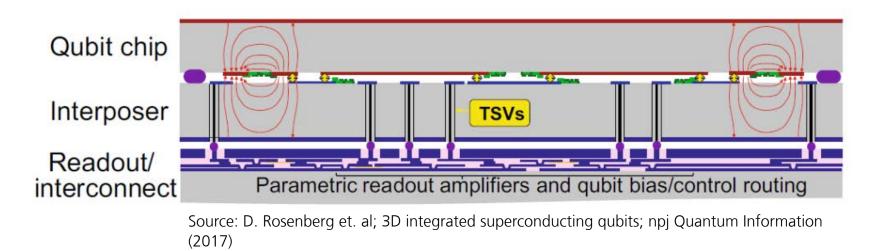

#### Application: Hybrid qPICs for Quantum Communication

Develop a Quantum System-on-Chip platform (QSoC)

#### Make Quantum Communication a Commodity

- Meterogeneous Integration for future projects (like MQV Bavaria) at Fraunhofer EMFT

- 3D Heterogeneous Integration for quantum systems

#### Challenges:

- Minimum Introduction of superconducting materials (e.g. In, NbN) for bump and TSV Technology

- Connection to metal lines on flex materials with respect to the cryogenic set-up

|            |                                    |    | A cooperation of | Leitriz<br>Ferdinand           |      |

|------------|------------------------------------|----|------------------|--------------------------------|------|

| 23.02.2022 | Fraunhofer EMFT (Dr. Lars Nebrich) | 25 |                  | Fordinand<br>Braun<br>Institut | i6p- |

|            |                                    |    |                  |                                |      |

- Building a strong European supply and value chain for new hardware for "Edge AI" applications requires a recognized, strong research alliance

- The Alliance for a "Testing and Experimentation Facility for Edge AI" (TEF Edge AI) provides affordable, fast access for small and medium-sized enterprises and system houses

- Development of necessary hardware technologies and new components to support energyefficient "green" AI applications ("Get AI off the cloud")

- Ø Open platform for other European partners (excellence and complementarity criteria)

- New European Commission funding programs (2021-2028): "Horizon Europe" (including Key Digital Technologies JU) and "Digital Europe" (program to boost digitalization in Europe)

26

MIKROELEKTRONIK

#### Heterogeneous Integration

Conclusion

- % Co-Design

- <sup>®</sup> Chip design needs a close link to the package design to guarantee high performance and reliability

- Multiple domains with different scaling properties have to be considered

- Different design libraries are necessary for product development

- Thermal, mechanical and electrical analysis are the key for high yield

- New Materials

- Mechanical, electrical and thermal interactions of different materials not yet used as default

- Cost

- Complex systems require new packages

- → Therefore new package platforms like embedding have to be considered

- Customer Requirements

- Reliability and application specific requirements

- # High performance is mostly required in HI-applications

- Control of temperature requires advanced cooling concepts

- # Test

- Mainto Application specific tests for complex packages (incl. mixed signal, media, etc.)

- # Electrical, mechanical and thermal aspects are important

#### **Direct Contact**

#### Spokesman of the Fraunhofer Group for Microelectronics Chairman of the FMD steering committee **Prof. Dr. Albert Heuberger** +49 9131 776 1000

+49 9131 776 1000 albert.heuberger@iis.fraunhofer.de

Advisor to the institute management Jan Plogsties +49 9131 776 1021 jan.plogsties@iis.fraunhofer.de

Head of the business office **Dr. Stephan Guttowski** +49 30 4005591 40 stephan.guttowski@mikroelektronik.fraunhofer.de

Referent of the business office **Marieke Lienert** +49 174 685 08 53 marieke.lienert@mikroelektronik.fraunhofer.de

Business Development Dr. Michael Töpper michael.toepper@mikroelektronik.fraunhofer.de

Technology Park Manager **Dr. Andreas Grimm** andreas.grimm@mikroelektronik.fraunhofer.de

Dr. Oliver Pyper oliver.pyper@mikroelektronik.fraunhofer.de

28