# **Ultra-Thin Chips**

# - A New Paradigm in Si Technology -

## Joachim N. Burghartz

INSTITUT FÜR MIKROELEKTRONIK STUTTGART

# Outline

- Ultra-thin chips: the paradigm shift

- Applications of ultra-thin chips

- Traditional, recent and potential future applications

- 3D ICs: Overcoming a bottleneck in CMOS scaling

- Systems-in-Foil (SiF): enabler for new applications

- Ultra-thin chip fabrication

- Post-process wafer thinning

- Thin chips based on SOI

- − Chipfilm<sup>™</sup> technology

- Characteristics of ultra-thin chips

- Warpage of thin chips

- Mechanical stability of thin chips

- Apparently anomalous piezoresistive effect

- Constraints for circuit design

- Conclusions

## Ultra-Thin vs. Thin Chips: the paradigm shift Ultra-Thin vs. Thin Chips: the paradigm shift

- Thick chips and wafers (conventional)

- 300 μm 1000 μm:

- Mechanically stiff and stable

- Thin chips and wafers (conventional)

- 100 μm 300 μm:

- Mechanically stiff with limited stability

- Reduced thermal resistance

- Ultra-thin chips and wafers

- 50 μm 100 μm:

- Limited stiffness and limited stability

- 10 μm 50 μm:

- Flexibile with good stability

- < 10 μm:

- Flexible with good stability

- Optically transparent

### **Properties of Ultra-Thin Chips and Wafers**

Mechanical

i inschips

- Warpage, curl-up

- Young's modulus may deviate from bulk-Si value!

- Rough edges, e.g. from dicing

- Rough backside, e.g. from polishing

- Topographic frontside from layer depositions

- Electrical

- Piezoresistive effect

- Backgate effects

- Optical

- Absorption spectrum limited

- Back-surface effects

- Thermal

- Bi-material displacement

### This chips Processing Issues for Ultra-Thin Wafers/Chips

- Front-end processes

- Handle/carrier substrates needed

- Overheating effects (high-dose implant, RTP)

- Back-end processes

- Excessive warpage from stress in interconnect layer stack

- Packaging and assembly

- Edge chipping in dicing processes

- Chip detachment from tape and transfer in assembly

- Chip attachment to package

- Mechanical pressure in wire bonding processes

# Outline

- Ultra-thin chips: the paradigm shift

- Applications of ultra-thin chips

- Traditional, recent and potential future applications

- 3D ICs: Overcoming a bottleneck in CMOS scaling

- Systems-in-Foil (SiF): enabler for new applications

- Ultra-thin chip fabrication

- Post-process wafer thinning

- Thin chips based on SOI

- Chipfilm<sup>™</sup> technology

- Characteristics of ultra-thin chips

- Warpage of thin chips

- Mechanical stability of thin chips

- Apparently anomalous piezoresistive effect

- Constraints for circuit design

- Conclusions

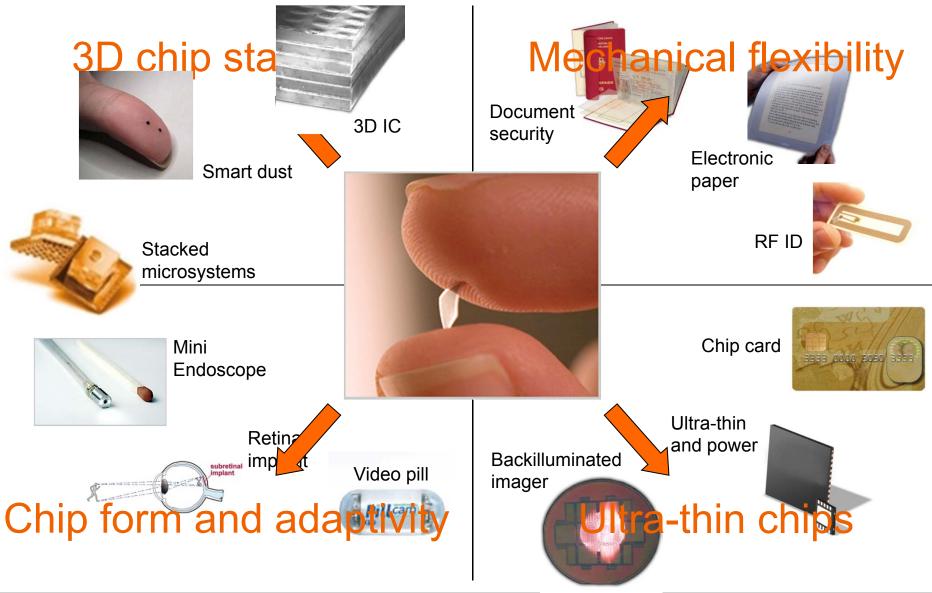

## **Applications of Ultra-Thin Chips**

i inschips

# Outline

- Ultra-thin chips: the paradigm shift

- Applications of ultra-thin chips

- Traditional, recent and potential future applications

- 3D ICs: Overcoming a bottleneck in CMOS scaling

- Systems-in-Foil (SiF): enabler for new applications

- Ultra-thin chip fabrication

- Post-process wafer thinning

- Thin chips based on SOI

- Chipfilm<sup>™</sup> technology

- Characteristics of ultra-thin chips

- Warpage of thin chips

- Mechanical stability of thin chips

- Apparently anomalous piezoresistive effect

- Constraints for circuit design

- Conclusions

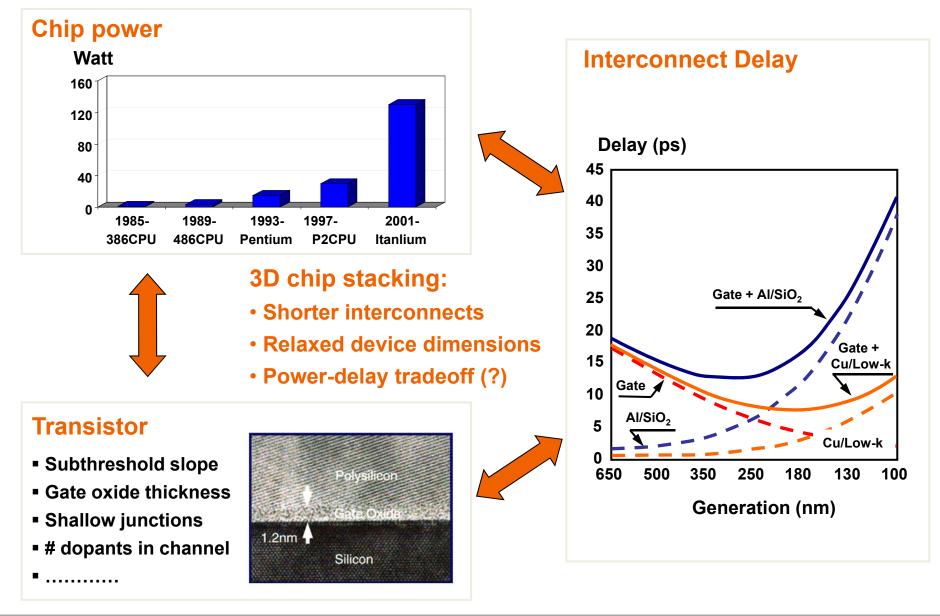

## **Bottlenecks in CMOS Scaling**

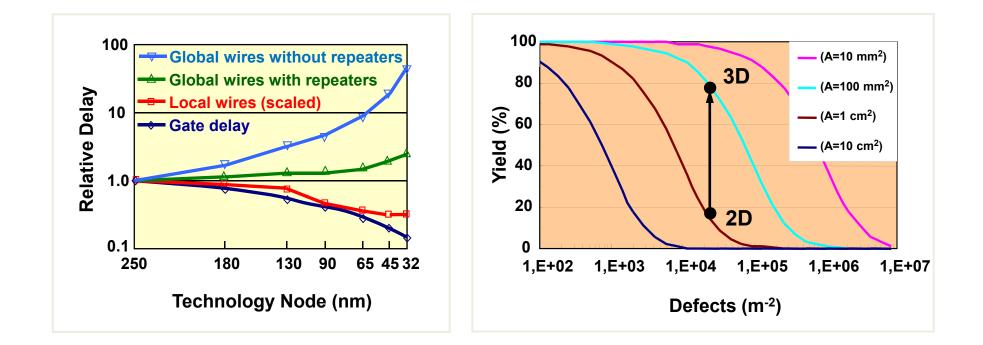

## **Interconnect Delay and Yield**

- Smaller interconnect RC delays through shorter wires !

- Higher process yield through smaller chip area !

i kinschips

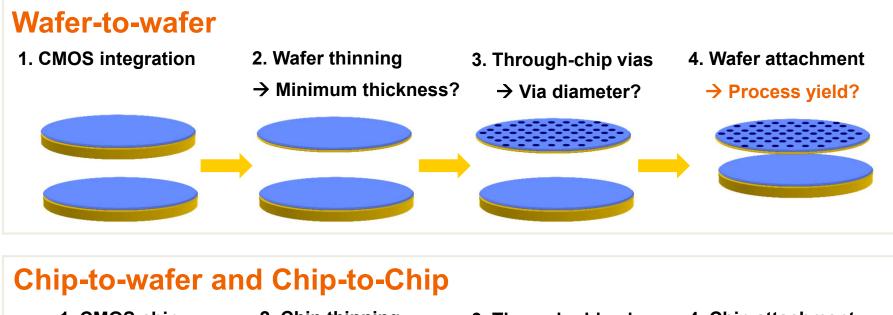

## **3D-IC Integration Concepts**

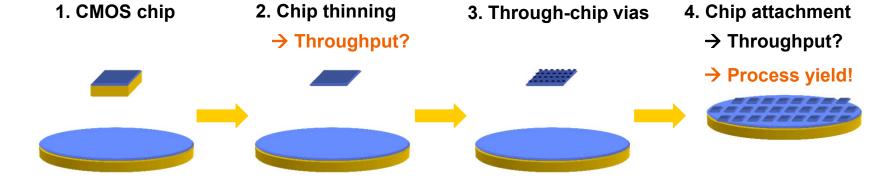

### Via Formation for VSI – *Via Metal Filling*

- More than 10:1 aspect ratio is difficult to achieve !

- Need for ultra-thin chips postulated on ITRS Roadmap

# Outline

- Ultra-thin chips: the paradigm shift

- Applications of ultra-thin chips

- Traditional, recent and potential future applications

- 3D ICs: Overcoming a bottleneck in CMOS scaling

#### - Systems-in-Foil (SiF): enabler for new applications

- Ultra-thin chip fabrication

- Post-process wafer thinning

- Thin chips based on SOI

- Chipfilm<sup>™</sup> technology

- Characteristics of ultra-thin chips

- Warpage of thin chips

- Mechanical stability of thin chips

- Apparently anomalous piezoresistive effect

- Constraints for circuit design

- Conclusions

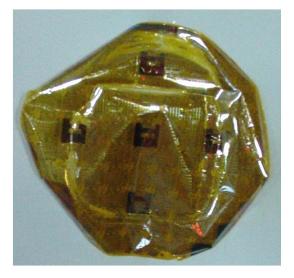

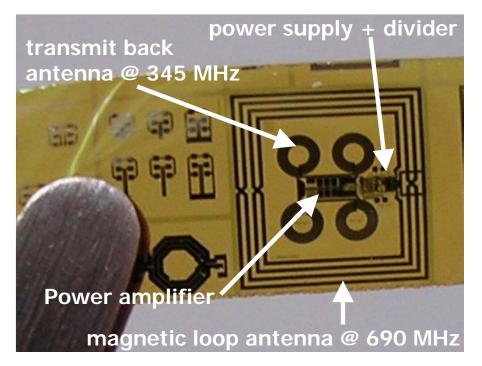

## **RF ID Tag**

#### **Department store sales**

#### Roll-to-roll assembly

#### Low-cost printing

14 Ultra-Thin Chips: A New Paradigm 2/11

### ePaper

### i his inschips

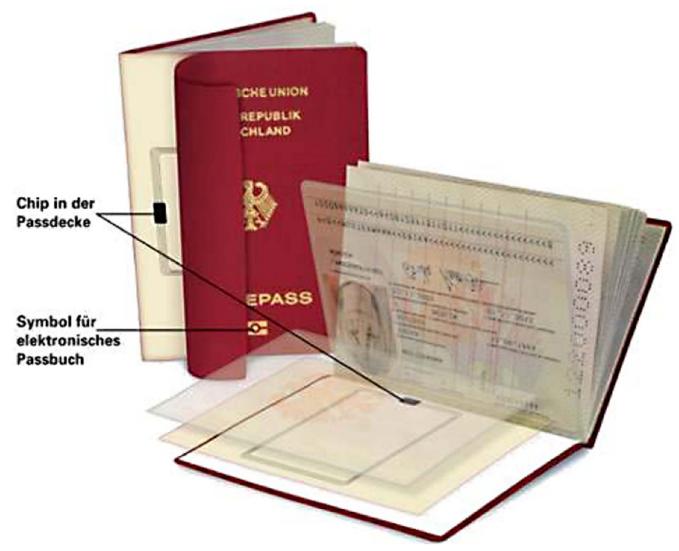

## **Document Security**

Source: NXP

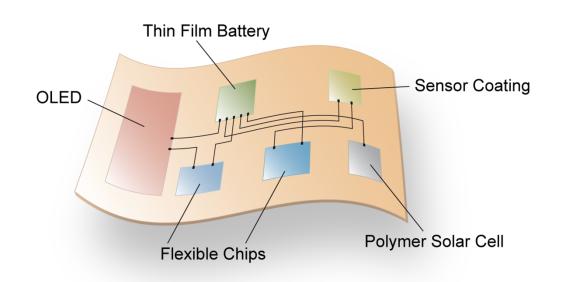

## **Hybrid Systems-in-Foil**

#### Si Circuit

#### Organic Circuit

#### → Hybrid systems-in-foil = combining technologies with complementary merits!

• Pro: thin, flexible chips !

Si Integration

+ • **Pro:** high integration

• Con: thick Si chips

• Con: devices on chip

**Thin Film Electronics**

• **Pro:** flexibility

• **Pro:** devices widely spaced

• **Con:** low integration density

# Outline

- Ultra-thin chips: the paradigm shift

- Applications of ultra-thin chips

- Traditional, recent and potential future applications

- 3D ICs: Overcoming a bottleneck in CMOS scaling

- Systems-in-Foil (SiF): enabler for new applications

#### Ultra-thin chip fabrication

- Post-process wafer thinning

- Thin chips based on SOI

- Chipfilm<sup>™</sup> technology

- Characteristics of ultra-thin chips

- Warpage of thin chips

- Mechanical stability of thin chips

- Apparently anomalous piezoresistive effect

- Constraints for circuit design

- Conclusions

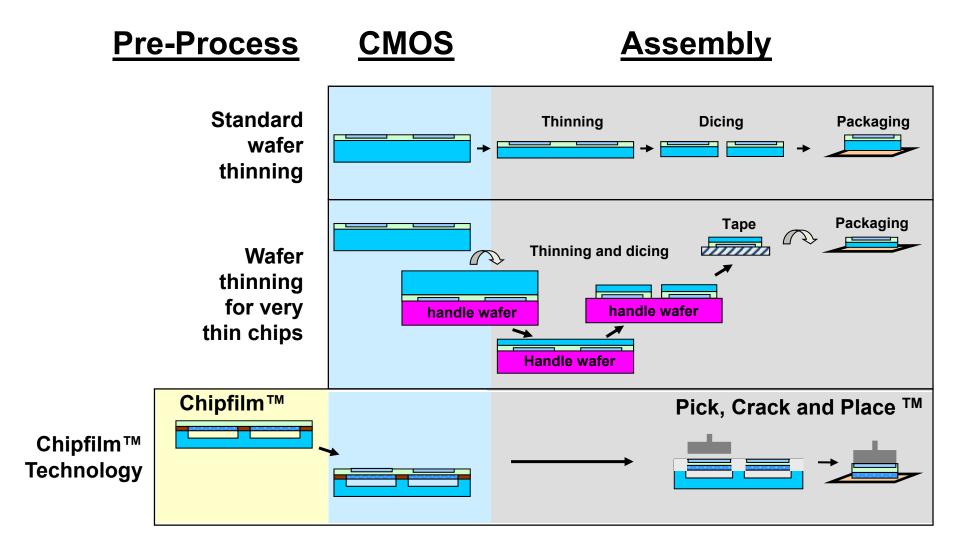

## **Process Technologies for Ultra-Thin Chips**

# Outline

- Ultra-thin chips: the paradigm shift

- Applications of ultra-thin chips

- Traditional, recent and potential future applications

- 3D ICs: Overcoming a bottleneck in CMOS scaling

- Systems-in-Foil (SiF): enabler for new applications

#### • Ultra-thin chip fabrication

- Post-process wafer thinning

- Thin chips based on SOI

- Chipfilm<sup>™</sup> technology

- Characteristics of ultra-thin chips

- Warpage of thin chips

- Mechanical stability of thin chips

- Apparently anomalous piezoresistive effect

- Constraints for circuit design

- Conclusions

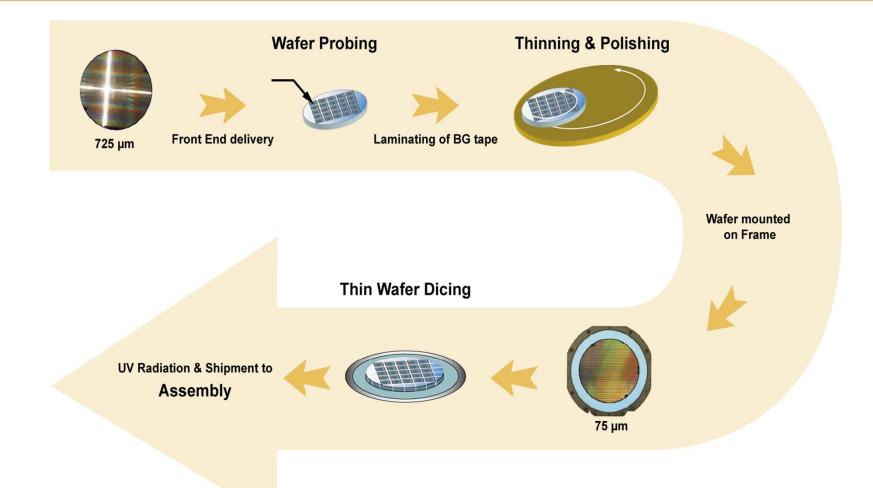

## نابعة Chips Wafer Back-Thinning: Process Sequence

#### $\rightarrow$ Economically practical wafer thickness >50 µm ! (NXP)

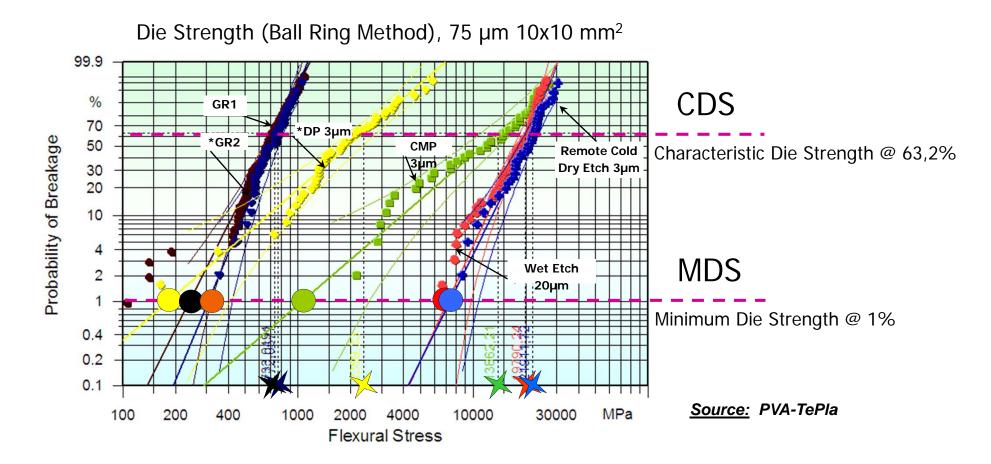

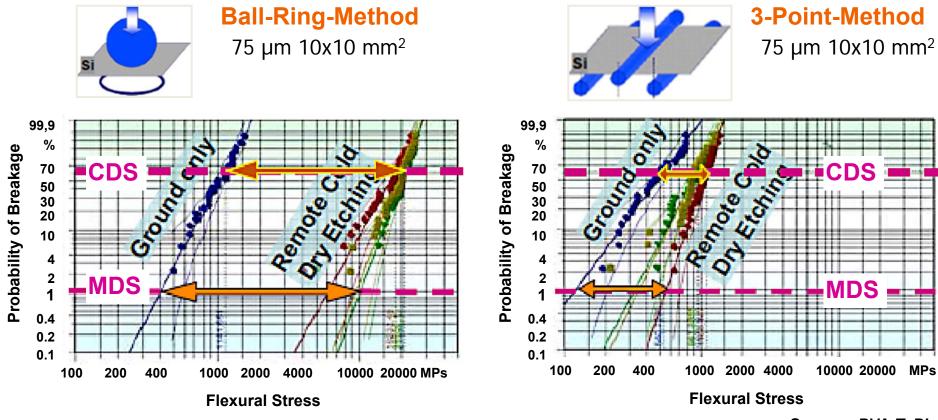

## نامة المعند Wafer Back-Thinning: Mechanical Stability

→ Fast grinding processes introduce more defects than slow etch processes

→ Combination of fast grinding followed by defect removal steps

## **Process Effects on Mechanical Stability**

Source: PVA-TePla

#### $\rightarrow$ Surface and edge quality of thin chips affect mechanical stability

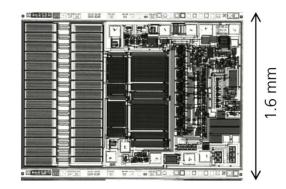

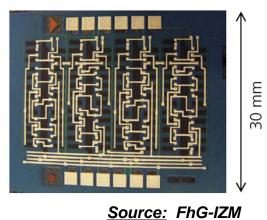

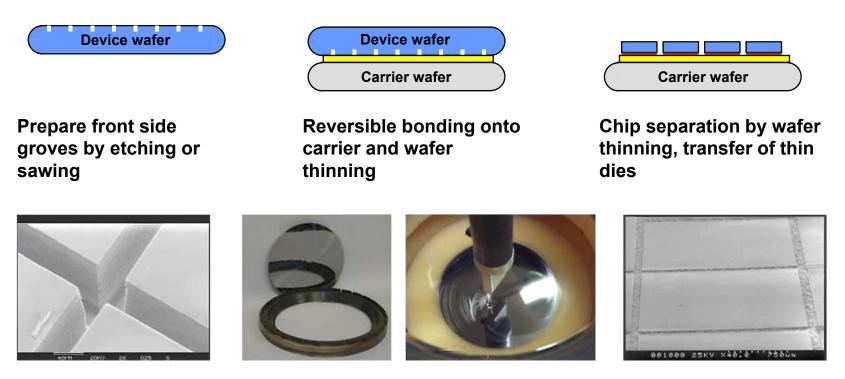

## **Dicing-by-Thinning concept DbyT"**

#### Manufacture and transfer of 20 µm thin chips

Wafer thinning: Grinding, etching, polishing

#### $\rightarrow$ Improved edge quality and thus mechanical stability

Source: FhG-IZM

i kinschips

# Outline

- Ultra-thin chips: the paradigm shift

- Applications of ultra-thin chips

- Traditional, recent and potential future applications

- 3D ICs: Overcoming a bottleneck in CMOS scaling

- Systems-in-Foil (SiF): enabler for new applications

#### Ultra-thin chip fabrication

- Post-process wafer thinning

- Thin chips based on SOI

- Chipfilm<sup>™</sup> technology

- Characteristics of ultra-thin chips

- Warpage of thin chips

- Mechanical stability of thin chips

- Apparently anomalous piezoresistive effect

- Constraints for circuit design

- Conclusions

# its inschips Philips's Circonflex Technology

#### Accidental detachment of Si-on-Glass Lead to Philips's Circonflex technology

Source: R. Dekker, Philips

# Outline

- Ultra-thin chips: the paradigm shift

- Applications of ultra-thin chips

- Traditional, recent and potential future applications

- 3D ICs: Overcoming a bottleneck in CMOS scaling

- Systems-in-Foil (SiF): enabler for new applications

#### Ultra-thin chip fabrication

- Post-process wafer thinning

- Thin chips based on SOI

- Chipfilm<sup>™</sup> technology

- Characteristics of ultra-thin chips

- Warpage of thin chips

- Mechanical stability of thin chips

- Apparently anomalous piezoresistive effect

- Constraints for circuit design

- Conclusions

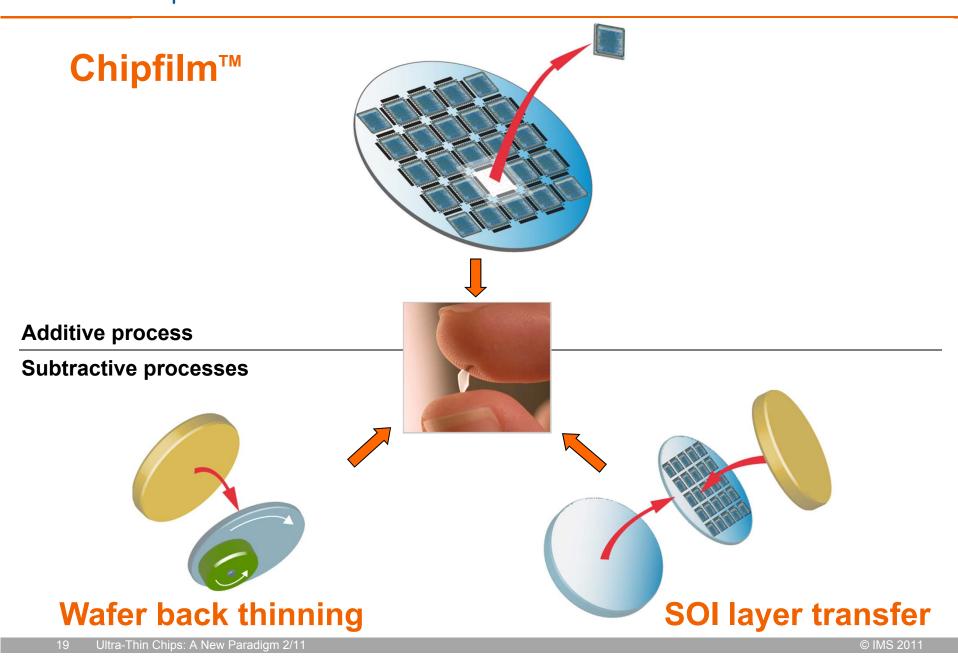

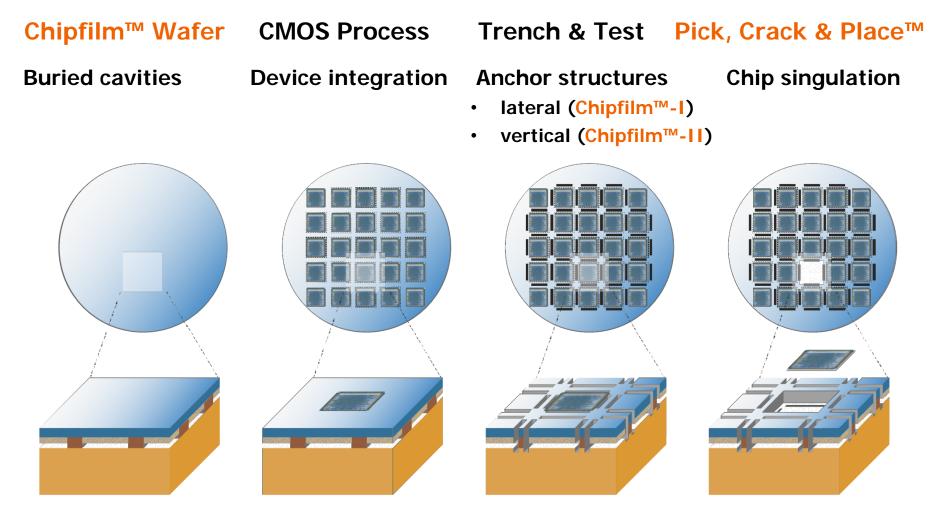

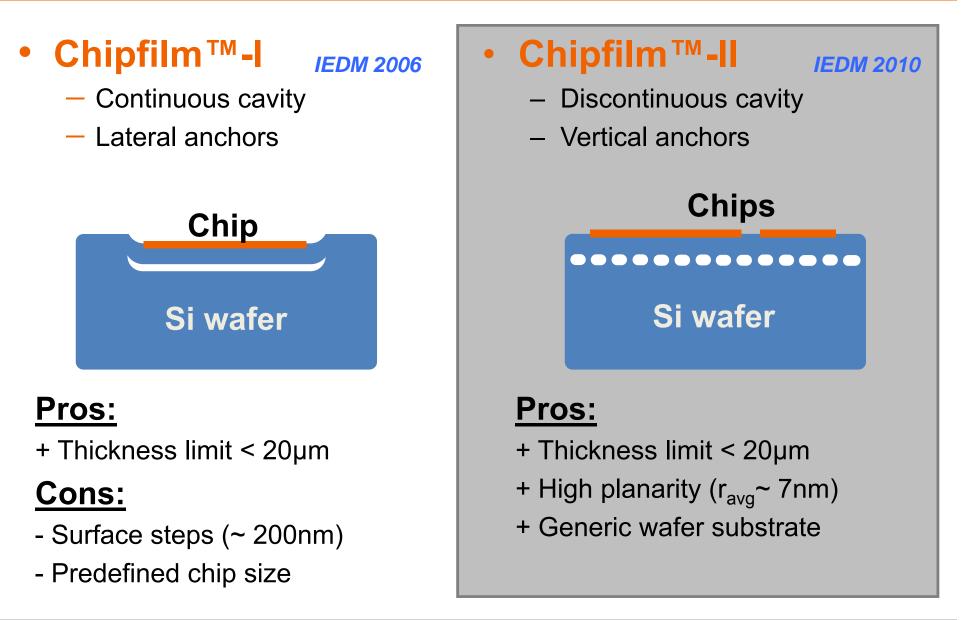

## **Chipfilm™ Technology**

IEDM 2006 Late News: Introduction of Chipfilm<sup>™</sup>-I IEDM 2010: Introduction of Chipfilm<sup>™</sup>-II

Since July 2008: Joint development with Robert Bosch GmbH

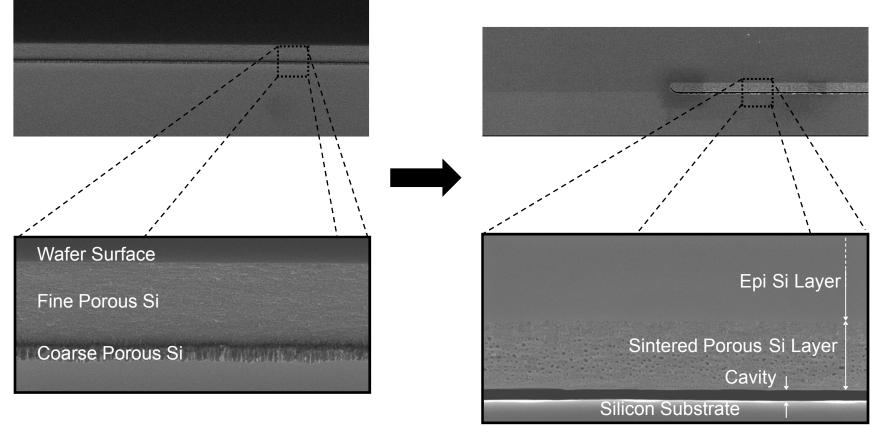

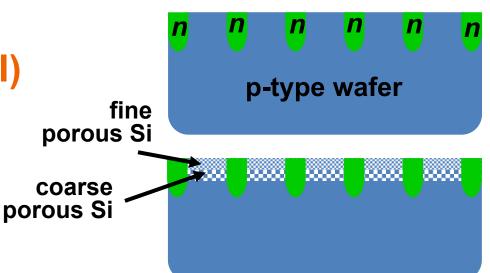

## **The Chipfilm<sup>™</sup> Pre-Process**

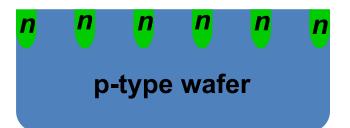

#### Step1:

- Anodic etching of a Si wafer

- Dual porous Si formation

- Masking through n<sup>+</sup> doping

#### <u>Step2:</u>

- Sintering in oxygen-free ambient

- Silicon reflow

- − Fine porous Si  $\rightarrow$  Nano grains

- Coarse porous Si  $\rightarrow$  Buried cavity

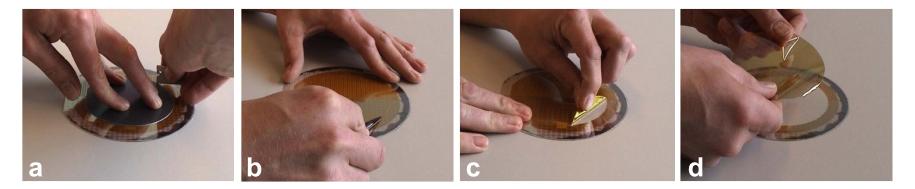

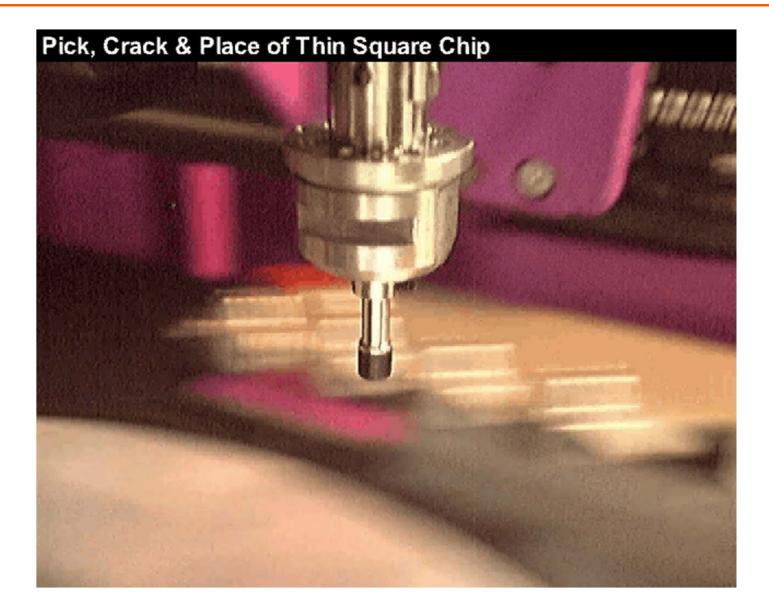

## לאביאה⊂ריוףה The Paick, Crack & Place™ Post-Process

## i ha inscrips

## **Technology Comparison**

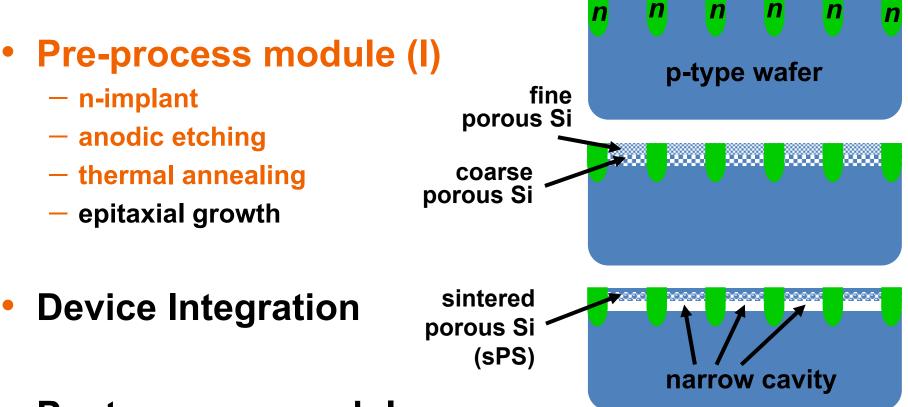

- Pre-process module (I)

- n-implant

- anodic etching

- thermal annealing

- epitaxial growth

- Device Integration

- Post-process module

- Trench etching

- Chip detachment

- Pre-process module (I)

- n-implant

- anodic etching

- thermal annealing

- epitaxial growth

- Device Integration

- Post-process module

- Trench etching

- Chip detachment

- Post-process module

- Trench etching

- Chip detachment